# MCR20A 2.4 GHz Low-Power Transceiver Reference Manual

Supports: MCR20AVHM

Document Number: MCR20ARM Rev. 3, July 2016

### Contents

### Section number

Title

Page

#### Chapter 1 Introduction to MCR20A

| 1.1  | Introduction                                             | 13 |

|------|----------------------------------------------------------|----|

| 1.2  | Block Diagram                                            | 14 |

| 1.3  | Modem Features Summary                                   | 15 |

| 1.4  | RF Interface and Usage                                   | 17 |

| 1.5  | Radio Architecture                                       | 17 |

|      | 1.5.1 Packet Structure                                   | 17 |

|      | 1.5.2 Receive Path Description                           | 17 |

|      | 1.5.3 Transmit Path Description                          | 18 |

| 1.6  | IEEE 802.15.4 Acceleration Hardware                      | 18 |

| 1.7  | Advanced Security Module (ASM) Overview                  | 19 |

| 1.8  | MCU Interface with SPI Overview                          | 20 |

|      | 1.8.1 Transceiver Control Overview                       | 21 |

| 1.9  | Clock Output, RF Control, and GPIO Summary               | 22 |

|      | 1.9.1 CLK_OUT Reference                                  | 22 |

|      | 1.9.2 RF Control Signals                                 | 22 |

|      | 1.9.3 Antenna Diversity                                  | 23 |

|      | 1.9.4 General Purpose Input Output (GPIO)                | 23 |

| 1.10 | Modem Operational Modes                                  | 23 |

| 1.11 | External PA and LNA                                      | 24 |

|      | Chapter 2<br>Signal Multiplexing and Signal Descriptions |    |

| 2.1  | Pin assignments                                          | 25 |

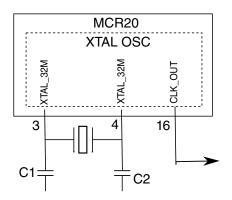

| 2.2  | Pin function table                                       | 26 |

#### Chapter 3 System Considerations

| Section number |        | number Title                                                 | Page |

|----------------|--------|--------------------------------------------------------------|------|

| 3.2            | Power  | Connections                                                  |      |

| 3.3            | Moder  | n Reset                                                      |      |

| 3.4            | Moder  | n Interrupt Request to MCU                                   |      |

| 3.5            | MCR2   | 20A Transceiver Interface to MCU                             |      |

|                | 3.5.1  | SPI Command Channel                                          |      |

| 3.6            | System | n Oscillator and Clock Considerations                        |      |

|                | 3.6.1  | Modem Crystal Oscillator                                     |      |

|                | 3.6.2  | System Clock Configurations                                  |      |

|                | 3.6.3  | Single System Crystal with CLK_OUT driving MCU crystal input |      |

| 3.7            | Moder  | n GPIO Characteristics                                       |      |

| 3.8            | MCR2   | 20A Digital Signal Properties Summary                        |      |

| 3.9            | Transc | eiver RF Configurations and External Connections             |      |

|                | 3.9.1  | RF Interface Pins                                            |      |

|                | 3.9.2  | RF Output Power Distribution                                 |      |

|                | 3.9.3  | LQI ED RSSI                                                  |      |

| 3.10           | Timer  | Resources                                                    |      |

|                | 3.10.1 | Modem Event Timer                                            |      |

| 3.11           | Low P  | Power Considerations                                         | 46   |

|                | 3.11.1 | Low-Power Preamble Search (LPPS)                             |      |

|                | 3.11.2 | Recovery Times from Low Power Modes                          |      |

|                | 3.11.3 | Run Time Current                                             |      |

|                |        | Chapter 4<br>Modem: Modes of Operation                       |      |

| 4.1            | Power  | Management Overview                                          |      |

|     | 4.1.1 | Features                      | 52  |

|-----|-------|-------------------------------|-----|

|     | 4.1.2 | Power and Regulation Topology | .52 |

|     | 4.1.3 | Digital Regulator and POR     | 53  |

|     | 4.1.4 | Analog Regulator (AREG)       | .53 |

| 4.2 | Moden | n Operational Modes Summary   | .54 |

|     | 4.2.1  | Power modes                                   |    |

|-----|--------|-----------------------------------------------|----|

| 4.3 | Seque  | nce Manager                                   |    |

|     | 4.3.1  | Modem Sequence Manager Operation              |    |

|     | 4.3.2  | Functional Description                        |    |

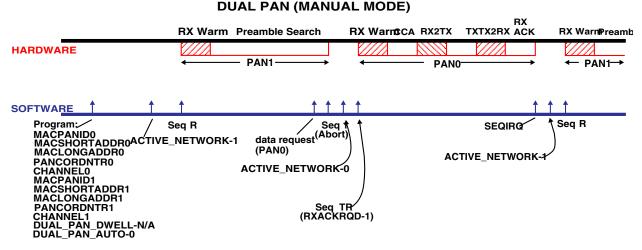

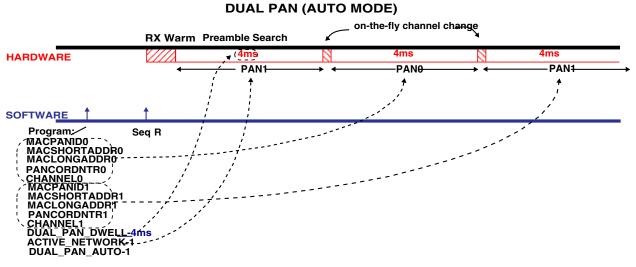

| 4.4 | Dual I | PAN ID introduction                           |    |

|     | 4.4.1  | Manual and Automatic Modes                    |    |

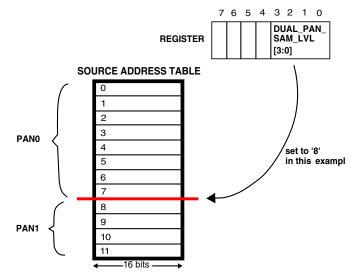

|     | 4.4.2  | Source Address Matching                       | 75 |

|     | 4.4.3  | Programming interface                         | 76 |

| 4.5 | Active | e Promiscuous Mode                            | 79 |

|     | 4.5.1  | Functional Description                        | 79 |

|     | 4.5.2  | Special Handling for Broadcast Packets        |    |

|     | 4.5.3  | Special Handling of Rx Acknowledgement Frames |    |

|     | 4.5.4  | Programming Interface                         |    |

| 4.6 | Clock  | System                                        |    |

|     | 4.6.1  | 32 MHz Crystal Oscillator                     |    |

|     | 4.6.2  | Clock output feature overview                 |    |

|     |        | Chapter 5<br>Modem: Advanced Security Module  |    |

| 5.1 | Advar  | nced Security Module                          |    |

| 5.2 | Introd | uction                                        |    |

Title

| 5.2 | muouu |                        |      |  |

|-----|-------|------------------------|------|--|

|     | 5.2.1 | Features               | 83   |  |

|     | 5.2.2 | Modes of Operation     | 83   |  |

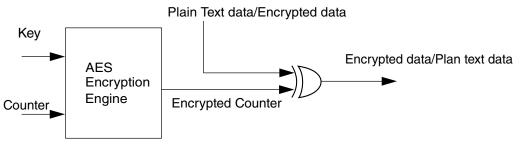

|     | 5.2.3 | CTR mode block diagram | 84   |  |

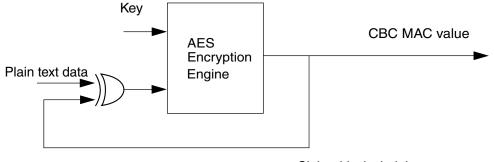

|     | 5.2.4 | CBC mode block diagram | .85  |  |

|     | 5.2.5 | CCM mode               | . 85 |  |

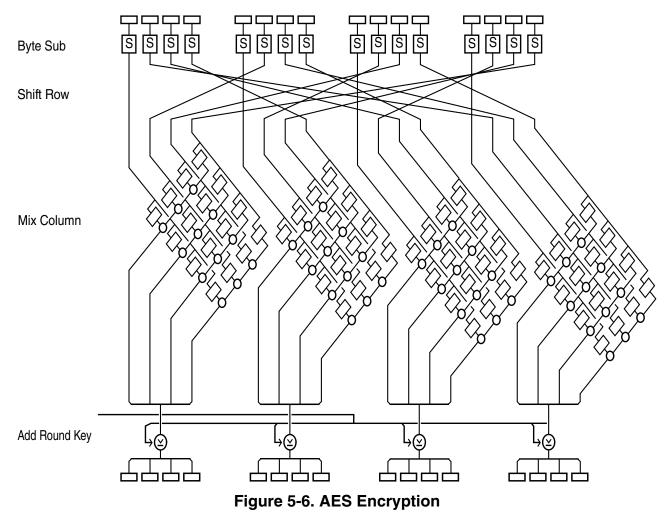

|     | 5.2.6 | AES mode               | 85   |  |

| 5.3 | ASM n | nodule block diagram   | .86  |  |

|     | 5.3.1 | ASM Register Interface | 86   |  |

|     | 5.3.2 | AES Encryption Engine  | 87   |  |

|     |       |                        |      |  |

### MCR20A 2.4 GHz Low-Power Transceiver Reference Manual, Rev. 3, July 2016

Section number

Page

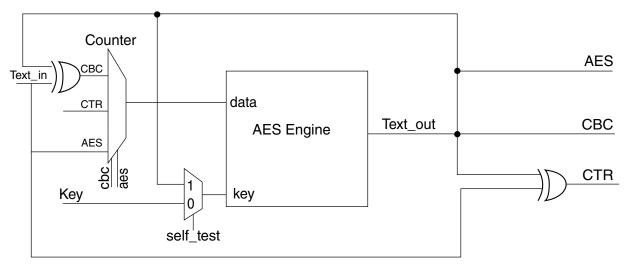

|     | 5.3.3  | ASM Logic                               | .87  |

|-----|--------|-----------------------------------------|------|

|     | 5.3.4  | AES encryption engine algorithm         | .88  |

| 5.4 | Counte | er mode encryption                      | .89  |

| 5.5 | AES n  | node encryption                         | . 89 |

| 5.6 | Messa  | ge Authentication Code generation (MAC) | .90  |

Title

#### Chapter 6 Modem: Interrupts

| Introdu | iction                                                                                                                                    | 91                                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Modem   | ı Interrupt Sources                                                                                                                       | . 91                                         |

| Additic | onal Interrupt Mask and Source Descriptions                                                                                               | . 93                                         |

| Functio | onal Description                                                                                                                          | 94                                           |

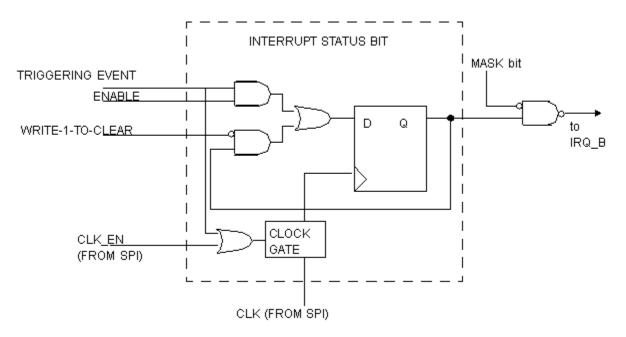

| 6.4.1   | Interrupt Status Bit Structure                                                                                                            | . 94                                         |

| 6.4.2   | Clearing Interrupts                                                                                                                       | . 95                                         |

| 6.4.3   | Timer Interrupts                                                                                                                          | . 95                                         |

| 6.4.4   | PLL Unlock Interrupt                                                                                                                      | 96                                           |

| 6.4.5   | Filterfail Interrupt                                                                                                                      | 96                                           |

| 6.4.6   | RX Watermark Interrupt                                                                                                                    | 97                                           |

| 6.4.7   | CCA Interrupt                                                                                                                             | . 97                                         |

| 6.4.8   | RX Interrupt                                                                                                                              | 98                                           |

| 6.4.9   | TX Interrupt                                                                                                                              | . 98                                         |

| 6.4.10  | Sequencer Interrupt                                                                                                                       | 98                                           |

| 6.4.11  | Interrupts from Exiting Low Power Modes                                                                                                   | 99                                           |

| 6.4.12  | Packet Buffer Error Interrupt                                                                                                             | 100                                          |

|         | Moden<br>Additio<br>Functio<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>6.4.9<br>6.4.10<br>6.4.11 | <ul> <li>6.4.2 Clearing Interrupts</li></ul> |

### Chapter 7 Modem: Timer Information

| 7.1 | Event Timer Block     | 101 |

|-----|-----------------------|-----|

| 7.2 | Event Timer Time Base | 101 |

| 7.3 | Setting Current Time  | 102 |

| 7.4 | Reading Current Time  | 103 |

#### MCR20A 2.4 GHz Low-Power Transceiver Reference Manual, Rev. 3, July 2016

Page

Section number

#### MCR20A 2.4 GHz Low-Power Transceiver Reference Manual, Rev. 3, July 2016

### Section number

7.5

7.6

7.7

| Latchi | ng the Timestamp                                            |     |

|--------|-------------------------------------------------------------|-----|

| Event  | Timer Comparators                                           |     |

| 7.6.1  | Timer Compare Fields                                        | 104 |

| 7.6.2  | Timer Compare-Enable Bits                                   |     |

| 7.6.3  | Timer Interrupt Status Bits                                 |     |

| 7.6.4  | Timer Interrupt Masks                                       | 105 |

| 7.6.5  | Setting Compare Values                                      |     |

| Intend | ed Event Timer Usage                                        | 106 |

| 7.7.1  | Generating Time-Based Interrupts                            |     |

| 7.7.2  | Using T3CMP to Abort an RX operation                        | 107 |

| 7.7.3  | Using T2CMP or T2PRIMECMP to Trigger Transceiver Operations |     |

Title

### Chapter 8 Modem SPI Interface

| 8.1 | Moden   | n SPI Overview                               | .111 |

|-----|---------|----------------------------------------------|------|

| 8.2 | Moden   | n SPI Basic Operation                        | 111  |

|     | 8.2.1   | SPI Pin Definition                           | 112  |

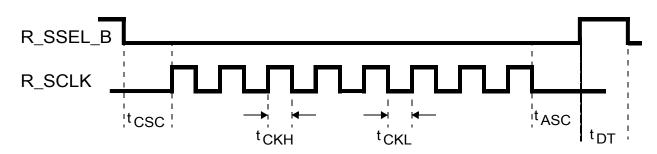

|     | 8.2.2   | SPI Timing                                   | 113  |

| 8.3 | SPI Tra | ansactions                                   | 114  |

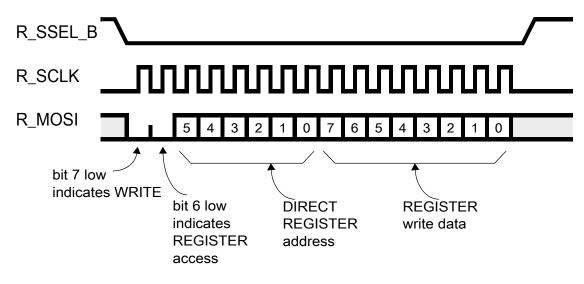

|     | 8.3.1   | SPI Control Word                             | .114 |

|     | 8.3.2   | Direct Register Write Access (single byte)   | 115  |

|     | 8.3.3   | Direct Register Read Access (single byte)    | .115 |

|     | 8.3.4   | Direct Register Write Access (multi byte)    | 116  |

|     | 8.3.5   | Direct Register Read Access (multi byte)     | 116  |

|     | 8.3.6   | Indirect Register Write Access (multi byte)  | 117  |

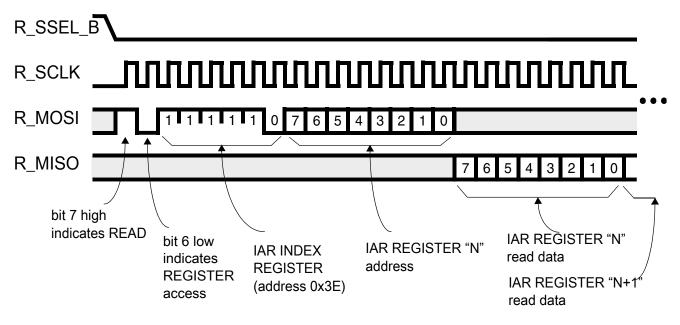

|     | 8.3.7   | Indirect Register Read Access (multi byte)   | 118  |

|     | 8.3.8   | Synchronous and Asynchronous Operating Modes | 118  |

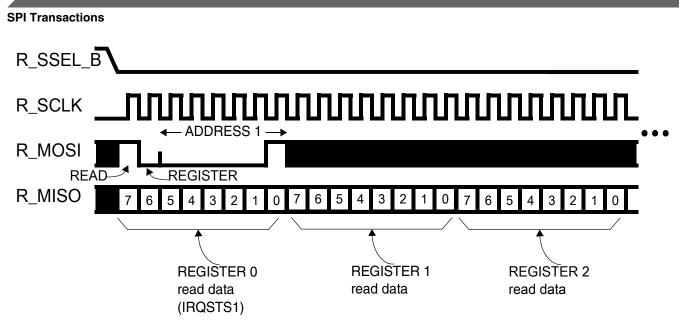

|     | 8.3.9   | Shifting Out IRQSTS1 During Control Word     | 119  |

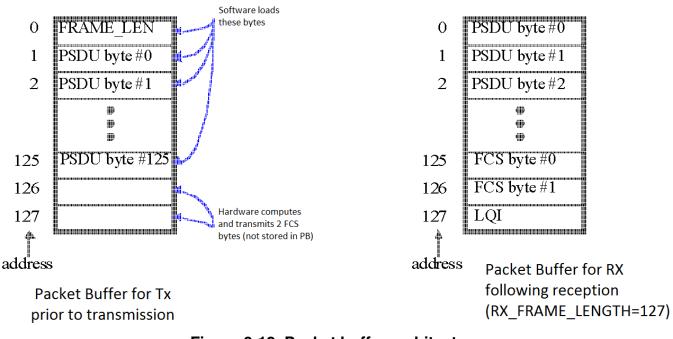

|     | 8.3.10  | Packet Buffer                                | .120 |

| 8.4 | Config  | uring MCU for Proper SPI Operation           | .128 |

### Page

| Sec | ction r | number Title                                           | Page |

|-----|---------|--------------------------------------------------------|------|

|     | 8.4.1   | DSPI Mode Configuration                                |      |

|     | 8.4.2   | DSPI Baud Rate                                         |      |

|     | 8.4.3   | DSPI Timing Control                                    |      |

|     |         | Chapter 9<br>Modem: SPI Register Description           | S    |

| 9.1 | Introdu | uction                                                 |      |

| 9.2 | Moder   | m Memory map and register definition                   |      |

|     | 9.2.1   | Interrupt Request Status 1 (Modem_IRQSTS1)             |      |

|     | 9.2.2   | Interrupt Request Status 2 (Modem_IRQSTS2)             |      |

|     | 9.2.3   | Interrupt Request Status 3 (Modem_IRQSTS3)             |      |

|     | 9.2.4   | PHY Control 1 (Modem_PHY_CTRL1)                        |      |

|     | 9.2.5   | PHY Control 2 (Modem_PHY_CTRL2)                        |      |

|     | 9.2.6   | PHY Control 3 (Modem_PHY_CTRL3)                        |      |

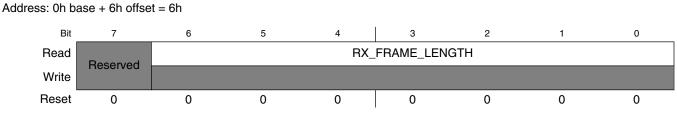

|     | 9.2.7   | Receive Frame Length (Modem_RX_FRM_LEN)                |      |

|     | 9.2.8   | PHY Control 4 (Modem_PHY_CTRL4)                        |      |

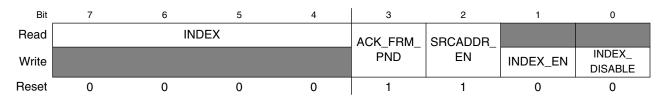

|     | 9.2.9   | SRC Control (Modem_SRC_CTRL)                           |      |

|     | 9.2.10  | SRC Address SUM LSB (Modem_SRC_ADDRS_SUM_LSB)          |      |

|     | 9.2.11  | SRC Address SUM MSB (Modem_SRC_ADDRS_SUM_MSB)          |      |

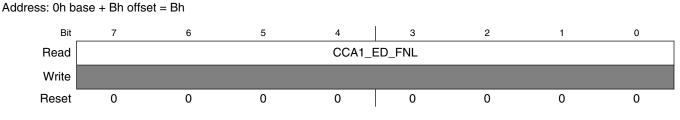

|     | 9.2.12  | CCA1 ED FNL (Modem_CCA1_ED_FNL)                        |      |

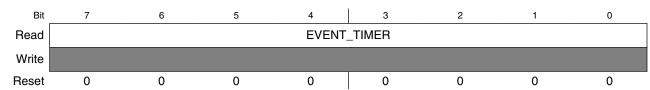

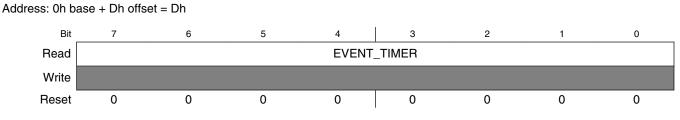

|     | 9.2.13  | Event Timer LSB (Modem_EVENT_TIMER_LSB)                |      |

|     | 9.2.14  | Event Timer MSB (Modem_EVENT_TIMER_MSB)                |      |

|     | 9.2.15  | Event Timer USB (Modem_EVENT_TIMER_USB)                |      |

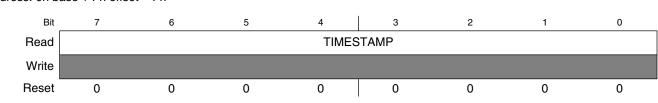

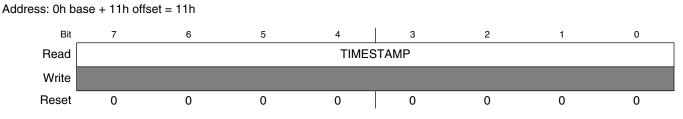

|     | 9.2.16  | Timestamp LSB (Modem_TIMESTAMP_LSB)                    |      |

|     | 9.2.17  | Timestamp MSB (Modem_TIMESTAMP_MSB)                    |      |

|     | 9.2.18  | Timestamp USB (Modem_TIMESTAMP_USB)                    |      |

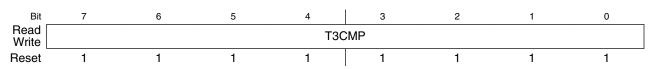

|     | 9.2.19  | Timer 3 Compare Value LSB (Modem_T3CMP_LSB)            |      |

|     | 9.2.20  | Timer 3 Compare Value MSB (Modem_T3CMP_MSB)            |      |

|     | 9.2.21  | Timer 3 Compare Value USB (Modem_T3CMP_USB)            |      |

|     | 9.2.22  | Timer 2-Prime Compare Value LSB (Modem_T2PRIMECMP_LSB) |      |

### Section number

### Title

### Page

|     | 9.2.23  | Timer 2-Prime Compare Value MSB (Modem_T2PRIMECMP_MSB)        | .150  |

|-----|---------|---------------------------------------------------------------|-------|

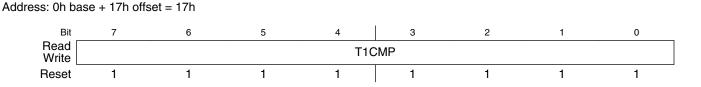

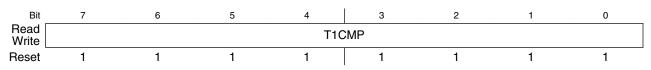

|     | 9.2.24  | Timer 1 Compare Value LSB (Modem_T1CMP_LSB)                   | . 150 |

|     | 9.2.25  | Timer 1 Compare Value MSB (Modem_T1CMP_MSB)                   | .151  |

|     | 9.2.26  | Timer 1 Compare Value USB (Modem_T1CMP_USB)                   | . 151 |

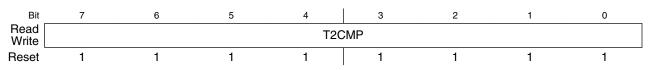

|     | 9.2.27  | Timer 2 Compare Value LSB (Modem_T2CMP_LSB)                   | . 151 |

|     | 9.2.28  | Timer 2 Compare Value MSB (Modem_T2CMP_MSB)                   | .152  |

|     | 9.2.29  | Timer 2 Compare Value USB (Modem_T2CMP_USB)                   | . 152 |

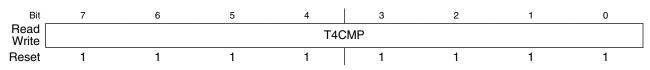

|     | 9.2.30  | Timer 4 Compare Value LSB (Modem_T4CMP_LSB)                   | . 152 |

|     | 9.2.31  | Timer 4 Compare Value MSB (Modem_T4CMP_MSB)                   | .153  |

|     | 9.2.32  | Timer 4 Compare Value USB (Modem_T4CMP_USB)                   | . 153 |

|     | 9.2.33  | PLL Integer Value for PAN0 (Modem_PLL_INT0)                   | . 153 |

|     | 9.2.34  | PLL Frequency Fractional Value for PAN0 (Modem_PLL_FRAC0_LSB) | . 154 |

|     | 9.2.35  | PLL Frequency Fractional Value for PAN0 (Modem_PLL_FRAC0_MSB) | . 154 |

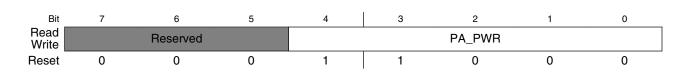

|     | 9.2.36  | PA Power Control (Modem_PA_PWR) (Modem_PA_PWR)                | 155   |

|     | 9.2.37  | Sequence Manager State (Modem_SEQ_STATE)                      | . 155 |

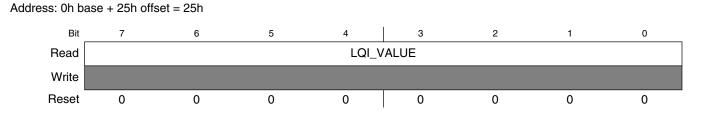

|     | 9.2.38  | Link Quality Indicator (Modem_LQI_VALUE)                      | 155   |

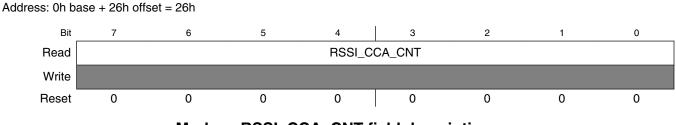

|     | 9.2.39  | RSSI CCA CNT (Modem_RSSI_CCA_CNT)                             | . 156 |

|     | 9.2.40  | ASM Control 1 (Modem_ASM_CTRL1)                               | .156  |

|     | 9.2.41  | ASM Control 2 (Modem_ASM_CTRL2)                               | .157  |

|     | 9.2.42  | ASM Data (Modem_ASM_DATA <i>n</i> )                           | .158  |

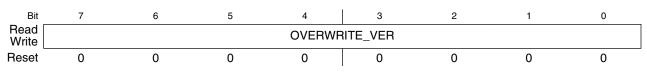

|     | 9.2.43  | Overwrite Version Number (Modem_OVERWRITE_VER)                | . 158 |

|     | 9.2.44  | CLK_OUT Control (Modem_CLK_OUT_CTRL)                          | .159  |

|     | 9.2.45  | Power Modes (Modem_PWR_MODES)                                 | . 160 |

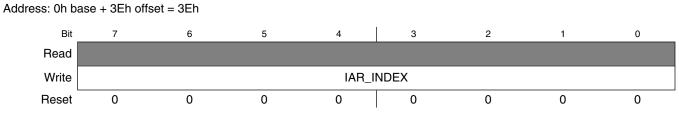

|     | 9.2.46  | IAR Index (Modem_IAR_INDEX)                                   | . 161 |

|     | 9.2.47  | IAR Data (Modem_IAR_DATA)                                     | . 162 |

| 9.3 | Indirec | t registers memory map and register definition                | . 162 |

|     | 9.3.1   | Part Identification (Indirect_Modem_PART_ID)                  | .165  |

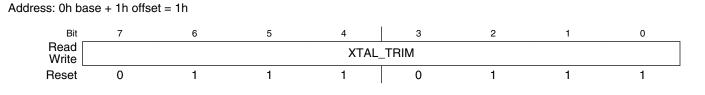

|     | 9.3.2   | XTAL 32 MHz Trim (Indirect_Modem_XTAL_TRIM)                   | .165  |

|     | 9.3.3   | MAC PAN ID for PAN0 (Indirect_Modem_MACPANID0n)               | .166  |

### Section number

### Title

### Page

| 9.3.4  | MAC Short Address for PAN0 (Indirect_Modem_MACSHORTADDRS0n)                           | 166 |

|--------|---------------------------------------------------------------------------------------|-----|

| 9.3.5  | MAC Long Address for PAN0 (Indirect_Modem_MACLONGADDRS0n)                             | 167 |

| 9.3.6  | Receive Frame Filter (Indirect_Modem_RX_FRAME_FILTER)                                 | 167 |

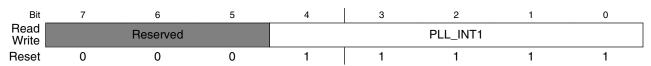

| 9.3.7  | Frequency Integer for PAN1 (Indirect_Modem_PLL_INT1)                                  | 168 |

| 9.3.8  | Frequency Fractional Value for PAN1 (Indirect_Modem_PLL_FRAC1n)                       | 169 |

| 9.3.9  | Frequency Fractional Value for PAN1 (Indirect_Modem_MACPANID1n)                       | 169 |

| 9.3.10 | MAC Short Address for PAN1 (Indirect_Modem_MACSHORTADDRS1n)                           | 170 |

| 9.3.11 | MAC Long Address for PAN1 (Indirect_Modem_MACLONGADDRS1n)                             | 170 |

| 9.3.12 | Dual PAN Control (Indirect_Modem_DUAL_PAN_CTRL)                                       | 171 |

| 9.3.13 | Channel Frequency Dwell Time (Indirect_Modem_DUAL_PAN_DWELL)                          | 172 |

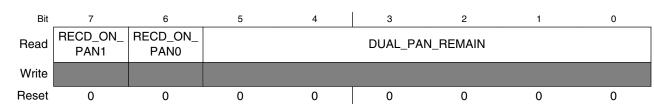

| 9.3.14 | Dual PAN Status (Indirect_Modem_DUAL_PAN_STS)                                         | 172 |

| 9.3.15 | Clear Channel Assessment 1 Threshold (Indirect_Modem_CCA1_THRESH)                     | 173 |

| 9.3.16 | Clear Channel Assessment / ED Offset Computation (Indirect_Modem_CCA1_ED_OFFSET_COMP) | 174 |

| 9.3.17 | LQI Offset Computation (Indirect_Modem_LQI_OFFSET_COMP)                               | 174 |

| 9.3.18 | CCA Control (Indirect_Modem_CCA_CTRL)                                                 | 174 |

| 9.3.19 | Clear Channel Assessment 2 Threshold Peak Compare (Indirect_Modem_CCA2_CORR_PEAKS)    | 175 |

| 9.3.20 | Clear Channel Assessment 2 Threshold (Indirect_Modem_CCA2_THRESH)                     | 176 |

| 9.3.21 | TMR PRESCALE (Indirect_Modem_TMR_PRESCALE)                                            | 176 |

| 9.3.22 | GPIO Data (Indirect_Modem_GPIO_DATA)                                                  | 177 |

| 9.3.23 | GPIO Direction Control (Indirect_Modem_GPIO_DIR)                                      | 178 |

| 9.3.24 | GPIO Pullup Enable (Indirect_Modem_GPIO_PUL_EN)                                       | 179 |

| 9.3.25 | GPIO Pullup Select (Indirect_Modem_GPIO_SEL)                                          | 181 |

| 9.3.26 | GPIO Drive Strength (Indirect_Modem_GPIO_DS)                                          | 182 |

| 9.3.27 | Antenna Control (Indirect_Modem_ANT_PAD_CTRL)                                         | 183 |

| 9.3.28 | Miscellaneous Pad Control (Indirect_Modem_MISC_PAD_CTRL)                              | 185 |

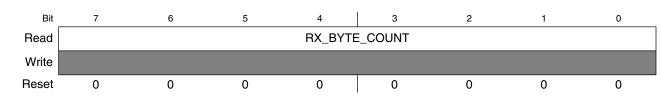

| 9.3.29 | RX_BYTE_COUNT (Indirect_Modem_RX_BYTE_COUNT)                                          | 185 |

| 9.3.30 | RX_WTR_MARK (Indirect_Modem_RX_WTR_MARK)                                              | 186 |

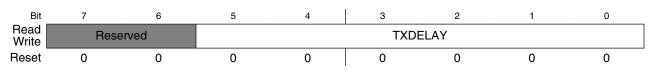

| 9.3.31 | TXDELAY (Indirect_Modem_TXDELAY)                                                      | 186 |

| 9.3.32 | ACKDELAY (Indirect_Modem_ACKDELAY)                                                    | 187 |

###

| 9.3.36 | XTAL | Control ( | Indirect_ | Modem_ | _XTAL_ | _CTRL) | 190 |

|--------|------|-----------|-----------|--------|--------|--------|-----|

## Chapter 1 Introduction to MCR20A

### 1.1 Introduction

The MCR20A transceiver is a 2.4 GHz Industrial, Scientific and Medical (ISM) and Medical Body Area Network (MBAN) transceiver intended for the IEEE® 802.15.4 Standard. The MCR20A device is a standalone transceiver that is normally combined with a software stack and a Kinetis K series, M series or other microcontroller (MCU) to implement an IEEE 802.15.4 Standard platform solution.

The MCR20A transceiver contains a complete 802.15.4 physical layer (PHY) modem designed for the IEEE® 802.15.4 Standard that operates in the 2.4 GHz ISM frequency band and supports 2.36 to 2.4 GHz Medical Band (MBAN) frequencies. The transceiver includes antenna diversity, 1mW nominal output power, hardware acceleration for dual PAN modes, integrated transmit/receive switch, on-board power supply regulation, and full spread-spectrum encoding and decoding. Additionally, the transceiver includes a PA with internal voltage controlled oscillator (VCO), integrated transmit/receive switch, on-board power supply regulation.

The MCR20A transceiver supports peer-to-peer, star, and mesh networking and when combined with an appropriate MCU, the MCR20A transceiver provides a cost-effective solution for short-range data links and networks. Interface with the MCU is accomplished using a four wire serial peripheral interface (SPI) connection and an interrupt request output that allows for the use of a variety of processors. The software and processor can be scaled to fit applications ranging from simple point-to-point systems through complete mesh networking. The MCR20A transceiver provides the IEEE 802.15.4 Standard PHY/MAC for use with the Kinetis K20 or Cortex M0 family of MCUs.

This table lists the MCR20A device ordering, temperature range, and package information.

#### **Block Diagram**

| Table 1-1. | Ordering | Information |

|------------|----------|-------------|

|------------|----------|-------------|

| Device       | Operating Temp Range<br>(TA) | Package                    |

|--------------|------------------------------|----------------------------|

| MCR20AVHM(R) | -40° to 105° C               | MLGA-32 (R: tape and reel) |

Target markets include, but are not limited, to the following:

- Smart Energy

- Meter

- ESI (Energy Service Interface)

- IHD (In Home Display)

- Gateway

- Appliance

- PHEV (Plug-in Hybrid Electric Vehicle)

- Building Control and Home Automation

- Lighting

- HVAC

- Security

- Medical / Personal Health Care

- Patient Monitoring

- Institutional Care

- Industrial Control (3rd party stacks (Low PAN, ISA100, Wireless HART)

## 1.2 Block Diagram

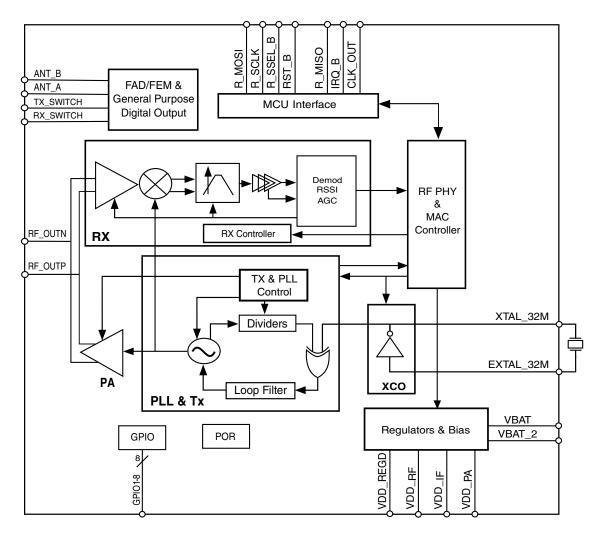

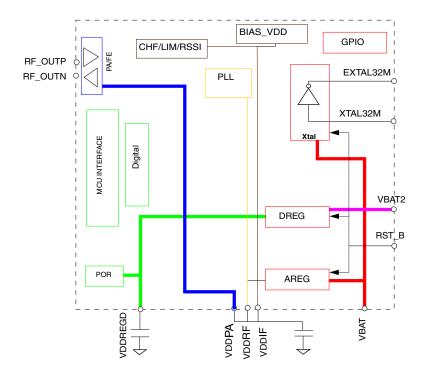

This figure shows a simplified block diagram of the MCR20A transceiver, which is an 802.15.4 Standard compatible transceiver that provides functions required in the physical layer (PHY) and media access control (MAC) specifications.

Figure 1-1. Modem Simplified Block Diagram

The modem is used in concert with an MCU. Interface between the devices is accomplished through a 4-wire SPI port and interrupt request line. The media access control (MAC), drivers, and network and application software (as required) reside on the host processor.

### **1.3 Modem Features Summary**

The transceiver has the following features:

• Fully compliant IEEE 802.15.4 Standard 2006 transceiver supports 250 kbps O-QPSK data in 5.0 MHz channels and full spread-spectrum encode and decode, and also extends radio operation to the 2.36 GHz to 2.40 GHz Medical Band (MBAN) frequencies with IEEE 802.15.4j channel, spacing and modulation requirements.

#### Modem Features Summary

- 2.4GHz frequency band of operation (ISM).

- 250kbps data rate with O-QPSK modulation in 5.0 MHz channels with direct sequence spread spectrum (DSSS) encode and decode.

- Operates on one of 16 selectable ISM channels per IEEE 802.15.4 specification.

- Programmable output power

- Supports 2.36 GHz to 2.40 GHz Medical Band (MBAN) frequencies with IEEE 802.15.4j channel, spacing and modulation requirements.

- Small RF foot print

- Differential input/output port used with external balun for single port operation.

- Supports antenna diversity operation with external front end (FE).

- Low external component count.

- Hardware acceleration for IEEE® 802.15.4 Standard

- Complete 802.15.4 onboard modem

- IEEE 802.15.4 Standard 2006 packet processor/sequencer with receiver frame filtering

- Random number generator

- Support for dual PAN ID mode

- Internal event timer block with four comparators to assist sequencer and provide timer capability

- 32 MHz crystal reference oscillator with onboard trim capability to supplement external load capacitors

- Programmable frequency clock output (CLK\_OUT) for use by MCU

- SPI Command Channel interface slave port with burst mode operation

- Interrupt request output (IRQ) provides interrupt request capability to MCU

- 128-byte RAM data buffer to store 802.15.4 packet contents for transceiver sequences

- Eight (8) software programmable GPIOs

- Low power operational modes with single SPI command device wake-up (SPI communication is enabled in LP mode)

- 1.8 V to 3.6 V operating voltage with on chip voltage regulators

- -40C to +105C temperature range

- RoHS compliant, 5 mm x 5 mm, 32-pin, MLGA package

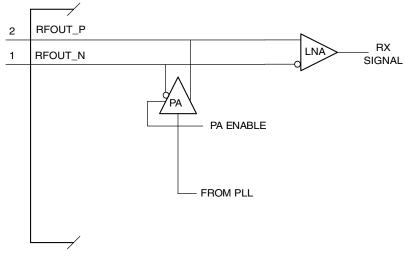

## 1.4 RF Interface and Usage

The modem RF interface provides a bidirectional, differential port that connects directly to a balun. The balun connects directly to a single-ended antenna and converts that interface to a fully differential, bidirectional, on-chip interface with transmit/receive switch, LNA, and complementary PA outputs. This combination allows for a small footprint and low cost RF solution.

In additional the modem provides dedicated output signals that can be used to control external RF components. These outputs are hardware switched and also support antenna diversity.

## 1.5 Radio Architecture

The radio structure is built upon the IEEE 802.15.4 Standard packet structure.

### 1.5.1 Packet Structure

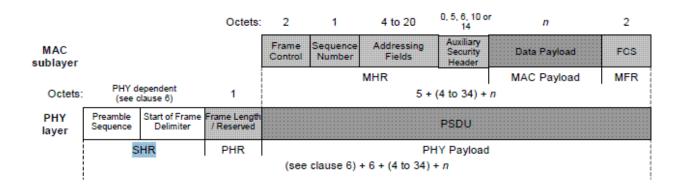

The following figure shows the packet structure.

| 4 bytes  | 1 byte | 1 byte | 125 bytes maximum | 2 bytes |

|----------|--------|--------|-------------------|---------|

| Preamble | SFD    | FLI    | Payload Data      | FCS     |

Figure 1-2. MCR20A Transceiver Packet Structure

### 1.5.2 Receive Path Description

The receive path operates in duplex with the transmit mode having an additional feature to operate in a low power run state that can also be considered as a partial power down mode. Architecture is Near Zero IF (NZIF) having front end amplification, one (1) mixed

signal down conversion to IF that is filtered, demodulated and digitally processed. The RF Front End (FE) is differential and shares the same off chip matching network with the transmit path.

### 1.5.3 Transmit Path Description

The modem transmits OQPSK modulation having power and channel selection adjustment per user application. After the channel of operation is determined, coarse and fine tuning is executed within the Frac-N PLL to engage signal lock. After signal lock is established, the modulated buffered signal is then routed to a multi-stage amplifier for transmission. The PA differential outputs share the pins with the front end.

## 1.6 IEEE 802.15.4 Acceleration Hardware

The 802.15.4 transceiver has several hardware features that reduce the software stack size, off-load functions from the CPU, and improve performance:

- Fully supports 2003 & 2006 versions of the IEEE 802.15 Standard.

- Supports slotted and unslotted modes

- Supports beacon enabled and non-beacon enabled networks

- Onboard 128-byte packet data buffering

- Random number generator

- 802.15.4 Sequence support

- RX (conditionally followed by TXAck)

- TX

- CCA (used for CCA and ED cycles)

- Tx/Rx (Tx followed by unconditional Rx or RCACK)

- Continuous CCA

- 802.15.4 Receiver Frame filtering.

### 1.7 Advanced Security Module (ASM) Overview

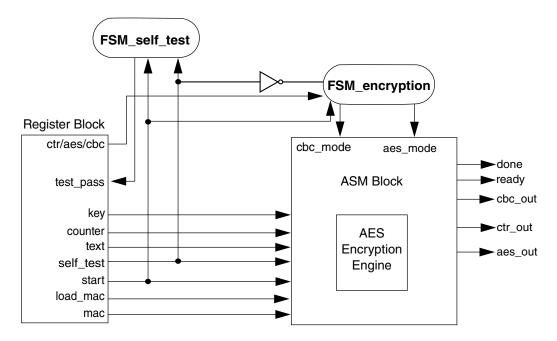

The ASM engine encrypts using the Advanced Encryption Standard (AES). It can perform "Counter" (CTR), Cipher Block Chaining (CBC) and plain AES mode encryption. The combination of CTR and CBC modes of encryption is known as CCM mode encryption. CCM is short for Counter with CBC-MAC. CCM is a generic authenticate and encrypt block cipher mode. CCM is only defined for use with 128 bit block ciphers, such as AES.

The ASM has the following features:

- CTR encryption in 11 bus clock cycles.

- CBC encryption in 11 bus clock cycles

- AES encryption in 11 bus clock cycles.

- Encrypts 128 bits as a unit.

The ASM is designed to be loaded with data and then started with a self-clearing "start" bit. Sixteen 8 bit registers of a key plus sixteen 8 bit registers of a counter plus sixteen 8 bit registers of text are necessary for "Counter" mode encryption. Cipher Block Chaining (CBC) mode needs only a key field and a text field programmed. Typically, only the text fields and counter fields need to be continuously written since the key field won't change.

The module has a built in self test that must be initiated by the software to make the module usable. Until this test is run and passes the ASM module is disabled.

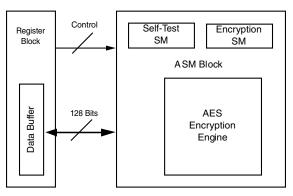

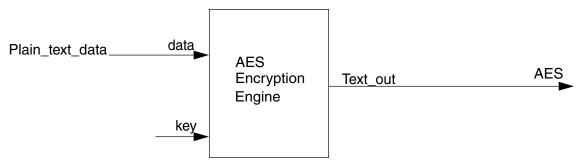

A simple block diagram of the ASM module is shown in the following figure.

Figure 1-3. ASM Block Diagram

## **1.8 MCU Interface with SPI Overview**

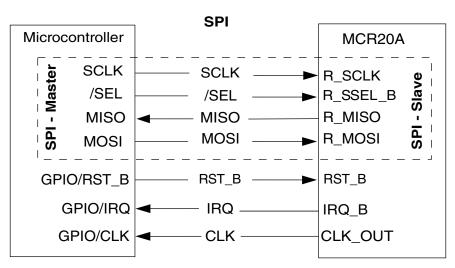

The following figure illustrates the microcontroller interface with the modem for the SiP. The typical required signals are:

- 4-wire SPI port slave mode only

- Maximum bitrate is 16 MHz for writes and 9 MHz for reads

- Clock phase and polarity CPHA=0 and CPOL=0

- MSB first shifting

- Supports Register Access and Packet Buffer accesses in bursts of byte transfers

- Most registers and Packet Buffer accessible with crystal "on" or "off"

- Interrupt request output active low

- Device asynchronous hardware reset RST\_B active low

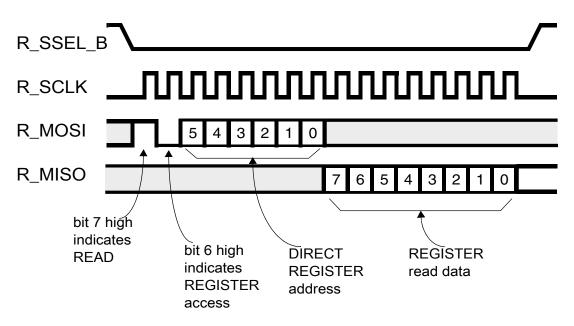

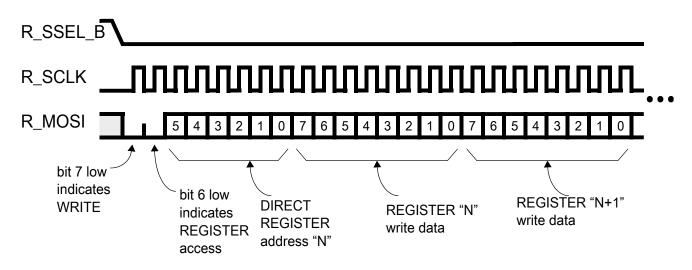

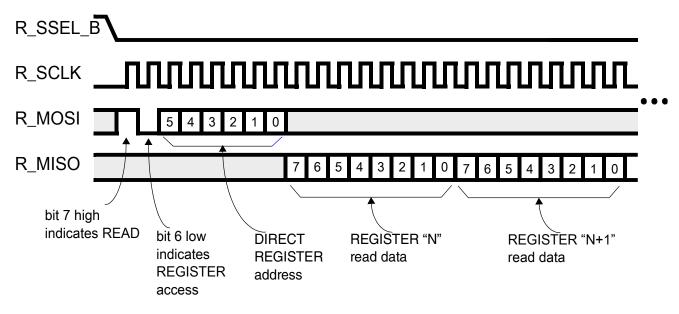

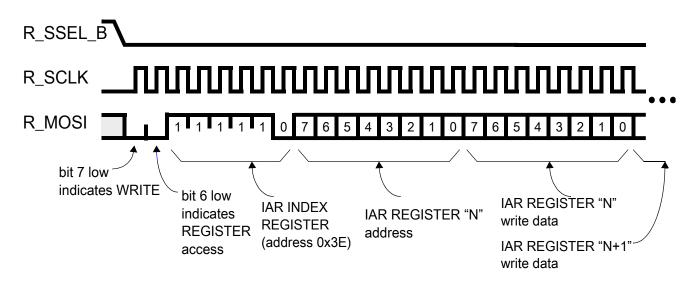

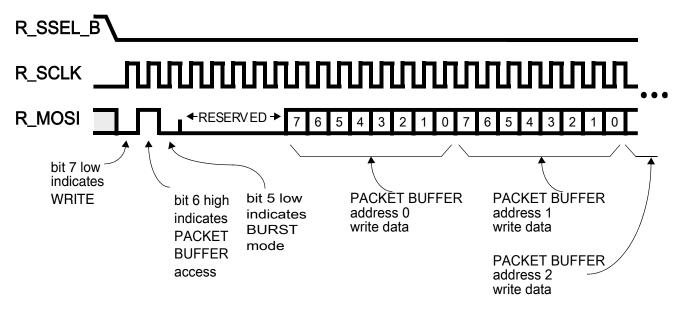

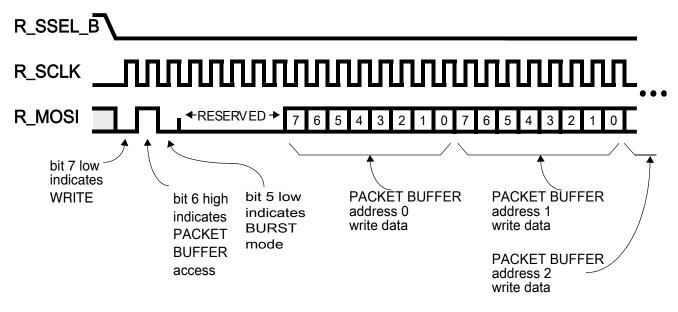

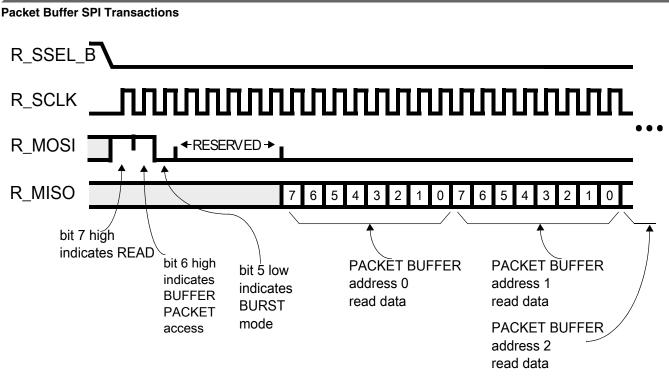

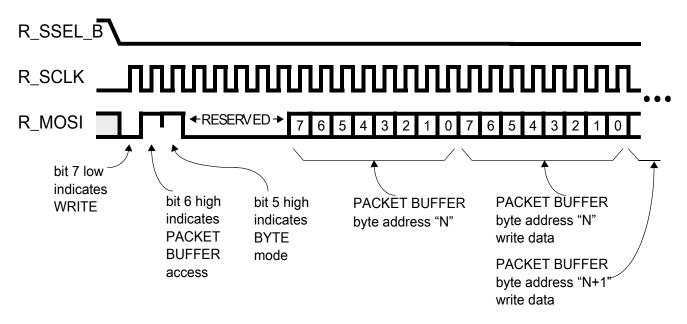

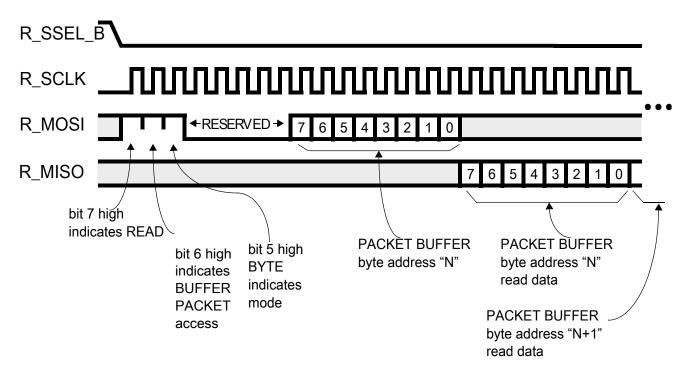

The SPI interface provides communication between the MCU and the modem's register set and Packet Buffer. The modem SPI is a slave-only interface; the MCU must drive R\_SSEL\_B, R\_SCLK and R\_MOSI. Write and read access to both Direct and Indirect registers is supported, and transfer length can be single-byte or bursts of unlimited length. Write and read access to the Packet buffer can also be single-byte or a burst mode of unlimited length.

The SPI interface is asynchronous to the rest of the device. No relationship between R\_SCLK and the modem's internal oscillator is assumed. All synchronization of the SPI interface to modem takes place inside the SPI module and is done for both register writes and reads.

The SPI is capable of operation in all power modes except reset. Operation in the Hibernate state means radio's crystal oscillator is disabled; effectively no XTAL connected in hibernate mode. Most radio registers, direct and indirect, can be accessed, both read and write, during Hibernate; and includes the complete Packet Buffer. All GPIO-related registers are accessible in Hibernate. In this state minimal power consumption will be realized especially during the register-initialization phase.

The SPI design features a compact, single-byte control word reducing SPI access latency to a minimum. Most SPI access types require only a single-byte control word with the address embedded in the control word. During control word transfer (the first byte of any

SPI access), the contents of the IRQSTS1 register (highest-priority status register) are are always shifted out so that the MCU gets access to IRQSTS1 with the minimum possible latency on every SPI access.

Figure 1-4. Microcontroller to modem interface block diagram

### **1.8.1 Transceiver Control Overview**

The transceiver is controlled by a bank of registers (Direct Register Space) accessed via the SPI interface. The transmit and receive packet data (stored in a 128-byte buffer) is also accessed via the SPI. The onboard registers provide control and status for the entire device.

### 1.8.1.1 Interrupt Request Overview

The modem has up to 13 individual sources of interrupt request to the MCU. These are all capable of individual control, and are logically OR-combined to drive a single, active low, interrupt request pin (IRQ\_B) to the external MCU.

- The IRQ\_B pin is configured as actively-driven high by the modem.

- Each interrupt source has its own interrupt status bit in Direct Register space.

- Each interrupt can be individually controlled by an interrupt mask The IRQ is issued when the mask is cleared to 0.

- There is also a global interrupt mask, TRCV\_MSK, which can enable/disable all IRQ\_B assertions by programming a single masking bit.

- All status bits use a write-1-to-clear protocol interrupt status bits are not affected by reads.

- IRQ\_B will remain asserted until all active interrupt sources are cleared or masked.

### 1.8.1.2 Event Timer Overview

The modem features a 24-bit Event Timer that can be used in conjunction with the sequencer to provide protocol control as well as timing interrupts. The Event Timer consists of a continuously running counter and four (4) separate 24-bit comparators:

- The Event Timer counter runs at the 802.15.4 bit rate of 250 kHz (programmable).

- Each comparator has an individual interrupt request capability the compare status is set when there is a match between the comparator and the timer counter. Each status can be enabled to generate an IRQ.

- In addition, a separate 16-bit T2PRIMECMP comparator is provided, which uses only the *lower 16 bits* of Event Timer, rather than require a full 24-bit compare.

## 1.9 Clock Output, RF Control, and GPIO Summary

The modem provides a set of I/O pins useful for supplying a system clock to the MCU, controlling external RF LNA/PA or antenna diversity circuitry and GPIO. The following sections discuss these options.

## 1.9.1 CLK\_OUT Reference

The CLK\_OUT digital output can be enabled to drive the system clock to the MCU. This provides a highly accurate clock source based on the transceiver reference oscillator. The clock is programmable over a wide range of frequencies divided down from its 32 MHz reference.

### 1.9.2 RF Control Signals

The modem provides four dedicated signals for control of external RF components. These signals designated as ANT\_A, ANT\_B, RX\_SWITCH, and TX\_SWITCH can be enabled to control external amplifiers, antenna switches, and other modules. When enabled they are switched via an internal hardware state machine. Typical uses include:

- Antenna diversity

- External PA

- External LNA

- T/R switching

## 1.9.3 Antenna Diversity

To improve the reliability of RF connectivity to long range applications, Antenna Diversity feature is supported without using the MCU through use of four dedicated control pins by direct register antenna selection. The digital regulator supplies bias to analog switches for control of external PA/LNA. These switches are programmable to sink and source two levels of current (2-3 mA and 10 mA) or can operate in a high impedance mode.

## 1.9.4 General Purpose Input Output (GPIO)

In addition eight (8) GPIO are provided for general use. Features for these pins include:

- Programmable output drive strength

- Programmable output slew rate

- Hi-Z mode

- Programmable as outputs or inputs (default)

- No IRQ capability

## 1.10 Modem Operational Modes

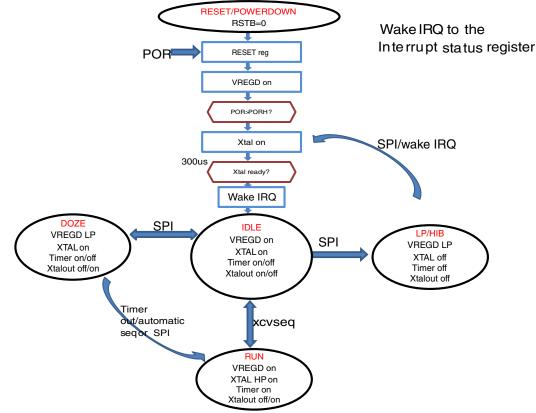

The modem has six operating modes which include:

#### External PA and LNA

- Reset / Power-down

- Low Power (LP) / Hibernate

- Doze (low power with reference oscillator active)

- Idle

- Receive

- Transmit

The following table describes these modes:

| Mode      | Definition                                                                                                          | Transition Time     |

|-----------|---------------------------------------------------------------------------------------------------------------------|---------------------|

| Mode      |                                                                                                                     | To or From Idle     |

| Off       | All modem functions Off, Leakage only. RST asserted. Digital outputs are tri-stated including IRQ                   | 500 µs              |

| Hibernate | Crystal Reference Oscillator Off. Modem responds to SPI activity.                                                   | 250 µs              |

| Doze      | Crystal reference oscillator ON but CLK_OUT output available only if selected. Digital regulator in Low Power mode. | < 1 µs <sup>1</sup> |

| Reset     | Crystal reference oscillator ON, enable CLK_OUT output at 4 MHz and 32.787 kHz.                                     | 376 µs              |

| Receive   | Crystal reference oscillator ON. Receiver ON.                                                                       | 144 µs              |

| Transmit  | Crystal reference oscillator ON. Transmitter ON.                                                                    | 144 µs              |

Table 1-2. Modem Mode Definitions and Transition Times

1. At 9 MHz, the doze to idle transistion time will be less than 2 SPI writes (1.8  $\mu s).$

### 1.11 External PA and LNA

The modem supports features to add either an external PA, LNA or RF switch which can extend the range or add antenna diversity to the target application. The following hardware features aid in the configuration of an FEM:

- Four dedicated programmable pins to sink and source 1mA, 2mA, 4mA and 8mA currents to control FEM (Front End Module) features such as a PA, LNA and RF switches for antenna diversity, etc.

- Balun used to optimize performance and provide a differential RX/TX output to single ended feature. Modem RX/TX outputs are differential "I" and "Q" and can be utilized in that format if desired.

## Chapter 2 Signal Multiplexing and Signal Descriptions

### 2.1 Pin assignments

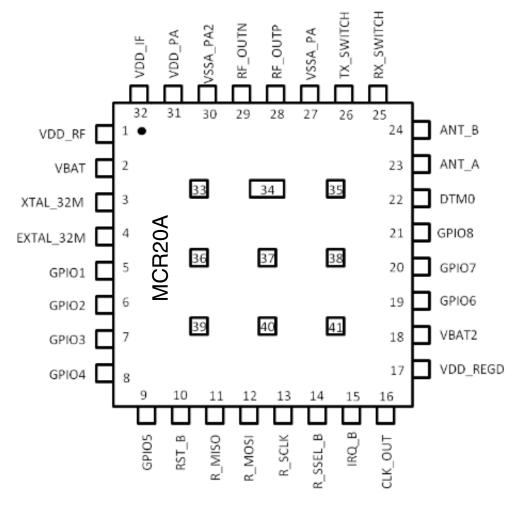

This figure shows the MCR20A transceiver's package pin assignment.

Figure 2-1. Pin assignment

## 2.2 Pin function table

| Pin<br>number | Pin name  | Туре                 | Function           | Description                                                                             |

|---------------|-----------|----------------------|--------------------|-----------------------------------------------------------------------------------------|

| 1             | VDD_RF    | Analog Power Output  | Analog Voltage     | Analog 1.8 Vdc                                                                          |

| 2             | VBAT      | Power Input          | Battery Voltage    | Connect to system VDD supply                                                            |

| 3             | XTAL_32M  | Analog Output        | RF                 | 32 MHz reference oscillator output                                                      |

| 4             | EXTAL_32M | Analog Input         | RF                 | 32 MHz references oscillator input                                                      |

| 5             | GPIO1     | Digital Input/Output | General-Purpose IO | GPIO                                                                                    |

| 6             | GPIO2     | Digital Input/Output | General-Purpose IO | GPIO                                                                                    |

| 7             | GPIO3     | Digital Input/Output | General-Purpose IO | GPIO                                                                                    |

| 8             | GPIO4     | Digital Input/Output | General-Purpose IO | GPIO                                                                                    |

| 9             | GPIO5     | Digital Input/Output | General-Purpose IO | GPIO or CLK_OUT default state select                                                    |

| 10            | RST_B     | Digital Input/Output | Digital            | Device asynchronous hardware reset. Active low.                                         |

| 11            | R_MISO    | Digital Input/Output | Digital            | SPI MISO                                                                                |

| 12            | R_MOSI    | Digital Input/Output | Digital            | SPI MOSI                                                                                |

| 13            | R_SCLK    | Digital Input/Output | Digital            | SPI clock                                                                               |

| 14            | R_SSEL_B  | Digital Input/Output | Digital            | SPI slave select                                                                        |

| 15            | IRQ_B     | Digital Input/Output | Digital            | Interrupt command signal                                                                |

| 16            | CLK_OUT   | Digital Output       | RF                 | Programmable clock source                                                               |

| 17            | VDD_REGD  | Digital Power Ref    | Digital Voltage    | Digital 1.8 Vdc ref. Decouple to ground.                                                |

| 18            | VBAT2     | Power Input          | Battery Voltage    | Connect to system VDD supply.                                                           |

| 19            | GPIO6     | Digital Input/Output | General-Purpose IO | GPIO                                                                                    |

| 20            | GPIO7     | Digital Input/Output | General-Purpose IO | GPIO                                                                                    |

| 21            | GPIO8     | Digital Input/Output | General-Purpose IO | GPIO                                                                                    |

| 22            | DTM0      | _                    | Factory Test       | Do not connect.                                                                         |

| 23            | ANT_A     | Digital Input/Output | Antenna Diversity  | Programmable sink and source<br>current output with selectable high<br>impedance state. |

| 24            | ANT_B     | Digital Input/Output | Antenna Diversity  | Programmable sink and source<br>current output with selectable high<br>impedance state. |

| 25            | RX_SWITCH | Digital Input/Output | Control Switch     | Programmable sink and source current output with selectable high impedance state.       |

| 26            | TX_SWITCH | Digital Input/Output | Control Switch     | Programmable sink and source current output with selectable high impedance state.       |

### Table 2-1. Pin function

Table continues on the next page...

**Chapter 2 Signal Multiplexing and Signal Descriptions**

| Pin<br>number | Pin name | Туре               | Function       | Description                            |

|---------------|----------|--------------------|----------------|----------------------------------------|

| 27            | VSSA_PA  | —                  | Gnd            | RF ground                              |

| 28            | RF_OUTP  | RFInput/Output     | RF             | Bidirectional RF input/output positive |

| 29            | RF_OUTN  | RFInput/Output     | RF             | Bidirectional RF input/output negative |

| 30            | VSSA_PA2 | —                  | Gnd            | RFground                               |

| 31            | VDD_PA   | Analog Power Input | Analog Voltage | Analog 1.8 Vdc input                   |

| 32            | VDD_IF   | Analog Power Input | Analog Voltage | Analog 1.8 Vdc input                   |

| 33            | GND_RF   | —                  | _              | Connect to RF ground                   |

| 34            | GND_PA   | —                  | _              | Connect to RF ground                   |

| 35            | GND_RF   | —                  | _              | Connect to RF ground                   |

| 36            | _        | Factory test       | Reserved       | Do not connect                         |

| 37            | _        | Factory test       | Reserved       | Do not connect                         |

| 38            | _        | Factory test       | Reserved       | Do not connect                         |

| 39            | —        | Factory test       | Reserved       | Do not connect                         |

| 40            | _        | Factory test       | Reserved       | Do not connect                         |

| 41            | _        | Factory test       | Reserved       | Do not connect                         |

Table 2-1. Pin function (continued)

MCR20A 2.4 GHz Low-Power Transceiver Reference Manual, Rev. 3, July 2016

## Chapter 3 System Considerations

### 3.1 Introduction

Communication to the modem function is through the common SPI bus, the MCU interrupt request, and several MCU GPIO lines. Primary interface with the modem is through the SPI command structure that allows reading/writing modem registers and provides initialization of parameters, reading of status, and control of modem operation. The modem can ask for real time response through the interrupt request structure, and four GPIO signals allow control of the modem reset and monitoring of some real time status.

This chapter presents information addressing application and operation of the node from a system level. The areas considered here are also covered in greater detail in the following sections of the book. The book is organized such that the first three chapters present the top-level view of the MCR20A device and the following chapters present individual functions in detailed descriptions.

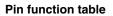

## 3.2 Power Connections

The modem power connections are listed in the following table.

| Pin Name | Туре         | Description                                   | Functionality       |

|----------|--------------|-----------------------------------------------|---------------------|

| VDD_RF   | Power Output | Regulator output for RF circuitry             | Decouple to ground. |

| VBAT     | Power Input  | Main voltage supply                           | Decouple to ground. |

| VDD_REGD | Power Output | Regulated output supply for digital circuitry | Decouple to ground  |

| VBAT2    | Power Input  | Main voltage supply                           | Decouple to ground. |

| GND_PA   | Power Input  | PA supply ground                              | Connect to ground   |

| GND_RF   | Power Input  | RF supply ground                              | Connect to ground   |

| VDD_PA   | Power Input  | Regulated supply for PA                       | Decouple to ground  |

Table 3-1. Power Pin Descriptions

Table continues on the next page...

| Pin Name | Туре        | Description             | Functionality      |

|----------|-------------|-------------------------|--------------------|

| VDD_IF   | Power Input | Regulated supply for IF | Decouple to ground |

| VSSA_PA  | Power Input | Common VSS              | Connect to ground  |

| VSSA_PA2 | Power Input | Common VSS              | Connect to ground  |

Table 3-1.

Power Pin Descriptions (continued)

When designing power to the device, the following points need to be considered for the modem:

- There are two modem primary power inputs, which include VBAT for analog power and VBAT2 for digital circuitry.

- For logic level compatibility between the modem and the system MCU, VBAT, and VBAT2 must be connected with the MCU to a common source supply of 1.8–3.6 VDC. It is not recommended to supply the MCU below 1.8V.

- VDD\_PA is the supply of the internal power amplifier and is powered by the VDD\_RF regulator output via the analog regulator.

- VDD\_RF and VDD\_IF are provided to allow bypass of the RF and IF circuitry regulated supplies. The decoupling capacitor is in the range of 220 nF and 470 nF as shown in the figure.

- The VDD\_REGD supply is decoupled externally as shown in the figure. The external decoupling capacitor shall be in the range of 220 nF and 470 nF.

Power supply connections for the modem are shown in the following figure.

Figure 3-1. Modem Power Supply Connections

### NOTE

In addition to the capacitor on the VBATs, there are two separate decoupling capacitors, one on VDD\_RF, VDD\_IF, and VDD\_PA that are tied together, and a standalone on VDD\_REGD.

## 3.3 Modem Reset

The modem active low reset input RST\_B is recommended to be driven from an MCU GPIO pin. In the interest of lowest power, there is no external pull-up resistor on input RST\_B. An MCU GPIO programmed as an output typically also has a software controlled pull-up resistor. However, it would normally not be used because the modem can be held in hardware reset by the MCU for extended periods of time. The transceiver IRQ pullup can also be disabled, and having no resistor makes for lowest power applications.

From a power-on or "cold start" condition, the MCU GPIO normally initiates as a highimpedance input with its internal pullup disabled and the IRQ pullup is enabled, which holds the modem reset input high. As part of the MCU initialization, GPIO must be programmed as an output and then driven low to reset the modem. The RST\_B input is asynchronous and needs to be held low for only a short period.

• The MCU software must configure one of its GPIOs as an output and then drive it low to reset the modem.

During the modem reset procedure,

- The MCU software should also configure the I/O port driving GPIO5 to select the default modem CLK\_OUT frequency (GPIO5 high = 32.787 kHz; GPIO5 low = 4 MHz).

- The modem RST\_B input is asynchronous and needs to be held low for only a short period.

In the reset condition, the modem is totally powered down and no clocks are available. After RST\_B is released, the modem will power up, initialize, and go to its idle condition in less than 1 millisecond, and in turn, this causes an IRQ\_B interrupt request and allows CLK\_OUT to start toggling. Coming out of reset, the WAKE\_IRQ interrupt status bit is set and causes the assertion on the IRQ\_B because the wake interrupt source is not masked by default.

Once the interrupt request is seen by the MCU, the MCU can assume the modem is alive and ready for programming via the SPI bus.

## 3.4 Modem Interrupt Request to MCU

The modem interrupt request IRQ\_B is an active low output that is asserted when an interrupt request is pending. The signal is released to high by writing a 1 to all asserted interrupt status bits in the modem status registers via a SPI transaction.

### 3.5 MCR20A Transceiver Interface to MCU

The modem interacts with the host MCU through its SPI interface, interrupt request, and several status and control signals.

### 3.5.1 SPI Command Channel

Primary interface with the modem is through the SPI command structure that allows reading/writing modem registers and provides initialization of parameters, reading of status, and control of modem operation. The modem is a slave only and the MCU SPI must be programmed and used as a master only. Further, the SPI performance is limited by the modem constraints of 8 MHz maximum SPI clock frequency, and use of the MCU SPI must be programmed to meet the modem SPI protocol. The SPI bus connections for a Kinetis K20-512 typically are:

- MCU MOSI output drives modem R\_MOSI.

- Modem R\_MISO output drives MCU MISO.

- MCU SCLK output drives modem R\_SCLK.

- MCU /SELoutput drives modem R\_SSEL\_B.

## 3.6 System Oscillator and Clock Considerations

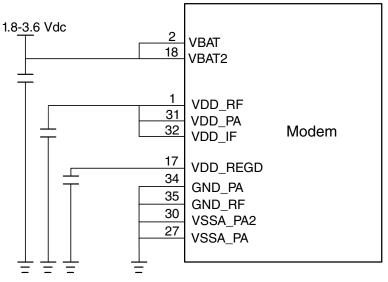

### 3.6.1 Modem Crystal Oscillator

The modem oscillator source must always be present and an external crystal is used to implement the oscillator. The source frequency must be 32 MHz with a total accuracy of  $\pm 40$  ppm or greater as required by the IEEE 802.15.4 specification.

In this figure, crystal X1 and capacitors C1 and C2 form the modem crystal oscillator circuit. An onboard feedback resistor of approximately 1 MOhm (not shown) between input EXTAL\_32M and output XTAL\_32M provides DC biasing for the oscillator buffer. An important parameter for the 32 MHz crystal X1 is a load capacitance of less than 9 pF. The oscillator needs to see a balanced load capacitance at each terminal of about 18 pF. As a result, the sum of the stray capacitance of the PCB, device pin (EXTAL or XTAL), and load capacitor (C1 or C2) at each terminal must equal about 18 pF. C1 and C2 are typically values of 6-9 pF. Higher values can load the crystal buffer and cause oscillator start-up problems.

The MCR20A transceiver crystal oscillator frequency can be trimmed by programming modem CLK\_OUT\_CTRL register to the corresponding wanted frequency and trim the frequency with the XTAL\_TRIM register. The trimming procedure varies the frequency by a few Hertz per step, depending on the type of crystal. As xtal\_trim[7:0] is increased, the frequency is decreased. This feature is useful for factory calibration of the crystal frequency to set the accuracy for the radio as required by the IEEE 802.15.4 specification.

Figure 3-2. MCR20A Oscillator and External Connections

## 3.6.2 System Clock Configurations

Because of the multiple clock configurations in an MCU and the CLK\_OUT output from the modem, there are a number of variations for system clock configurations. Key considerations for any system clock configuration are:

- The modem 32 MHz source (typically the crystal oscillator) must always be present. The crystal has special requirements and the reference frequency must meet IEEE 802.15.4 requirements

- Battery-operated application requirements for low power can impact the choices for MCU clock source

- The system clock configuration can impact system initialization procedures

- Software requirements can impact MCU processor and bus speed. The user must be aware of the performance requirements for the MCU.

# 3.6.3 Single System Crystal with CLK\_OUT driving MCU crystal input

The single crystal (modem crystal) with CLK\_OUT driving the MCU external clock input is a common configuration for low cost and excellent frequency accuracy. The CLK\_OUT frequency is programmable from 32.786 kHz to 32 MHz and drives the MCU external source.

### Note

For this system option to be usable, the system MCU must have an alternative (typically onboard) start-up clock.

In this configuration, clock start-up from a reset condition involves:

- MCU reset is released and MCU starts on an internal clock

- Initialization software must reset and then release reset to the modem (MCU still running on start-up clock)

- Wait for modem start-up interrupt request (less than 1 ms). CLK\_OUT default is hardware selectable as either 4 MHz or 32.786 kHz defined by the state of modem GPIO5.

- Program CLK\_OUT to a different frequency (if desired) as shown in the table.

- Wait for the CLK\_OUT source to lock, and then switch MCU clock to external source

Additional considerations for this mode of operation include:

- If the modem is forced to the Off condition and CLK\_OUT is killed, there is a 500 µs wait for the modem CLK\_OUT to start from the Off condition after RST is released

- If the MCU puts the modem into Doze mode, keeping the CLK\_OUT alive is a higher power, but available, option

- If an accurate period is required for longer time delays (such as a beacon period), keeping CLK alive for very long periods is an option, but would be a higher power option typically than using a separate crystal for the MCU

## 3.7 Modem GPIO Characteristics

The modem GPIO hardware consists of eight (8) signals total (GPIO1-GPIO8) though only GPIO1-6 are used in the SIP, and only GPIO1-2 are connected directly to SIP package pins. Immediately after reset, each GPIO has either an internal pull-up (GPIO1-5) or pull-down (GPIO6-8) enabled.

### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should change the direction of unused pins to outputs (programmed low) so the pins do not float. Outputs programmed low is the preferred option for lowest power.

The functionality of the modem GPIO is controlled by programming of the modem SPI registers via the SPI interface. For information about controlling all these pins as general purpose I/O pins, see SPI Register Descriptions chapter.

## 3.8 MCR20A Digital Signal Properties Summary

This table summarizes digital I/O pin characteristics. These characteristics are determined by the way the common pin interfaces are hard-wired to internal circuits.

| Pin Name      | Dir | Drive<br>Strength | Output Slew <sup>1</sup> | Pullup/<br>Pulldown <sup>2</sup> | Direction                                                                                                                                                                            |

|---------------|-----|-------------------|--------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ_B         | 0   | SWC               | Ν                        | Ν                                | Actively Driven output by default. Can be configured<br>as Open-drain (see IRQ_B_OD bit). Drive strength<br>controlled by NON_GPIO_DS bit.                                           |

| XTAL_32M      | I   |                   |                          | N                                |                                                                                                                                                                                      |

| EXTAL_32<br>M | 0   |                   |                          | Ν                                |                                                                                                                                                                                      |

| RST_B         | I   |                   |                          | Ν                                | Pin should not be allowed to float. Must be externally actively driven, or externally pulled up to Vbatt via resistor.                                                               |

| CLK_OUT       | 0   | SWC               | SWC                      | Ν                                | Drive strength controlled by CLK_OUT_DS bit. Slew<br>Rate controlled by CLK_OUT_SR bit. Tri-state<br>controlled by CLK_OUT_HIZ bit. Frequency controlled<br>by CLK_OUT_DIV[2:0] bits |

| R_SCLK        | I   |                   |                          | SWC                              | Pullup device controlled by SPI_PUL_EN bit                                                                                                                                           |

| R_MOSI        | I   |                   |                          | SWC                              | Pullup device controlled by SPI_PUL_EN bit                                                                                                                                           |

| R_MISO        | 0   | SWC               | N                        | Ν                                | Drive strength controlled by NON_GPIO_DS bit                                                                                                                                         |

| R_SSEL_B      | I   |                   |                          | SWC                              | Pullup device controlled by SPI_PUL_EN bit                                                                                                                                           |

| GPIO1         | I/O | SWC               | N                        | SWC                              | Drive strength controlled by GPIO_DS[1] bit. Pull<br>Enable/Polarity controlled by GPIO_PUL_EN[1] and<br>GPIO_PUL_SEL[1] bits.                                                       |

Table 3-2.

MCR20A Digital Signals Properties

Table continues on the next page ...

| Pin Name | Dir | Drive<br>Strength | Output Slew <sup>1</sup> | Pullup/<br>Pulldown <sup>2</sup> | Direction                                                                                                                      |

|----------|-----|-------------------|--------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| GPIO2    | I/O | SWC               | Ν                        | SWC                              | Drive strength controlled by GPIO_DS[2] bit. Pull<br>Enable/Polarity controlled by GPIO_PUL_EN[2] and<br>GPIO_PUL_SEL[2] bits. |

| GPIO3    | I/O | SWC               | Ν                        | SWC                              | Drive strength controlled by GPIO_DS[3] bit. Pull<br>Enable/Polarity controlled by GPIO_PUL_EN[3] and<br>GPIO_PUL_SEL[3] bits. |

| GPIO4    | I/O | SWC               | Ν                        | SWC                              | Drive strength controlled by GPIO_DS[4] bit. Pull<br>Enable/Polarity controlled by GPIO_PUL_EN[4] and<br>GPIO_PUL_SEL[4] bits. |

| GPIO5    | I/O | SWC               | Ν                        | SWC                              | Drive strength controlled by GPIO_DS[5] bit. Pull<br>Enable/Polarity controlled by GPIO_PUL_EN[5] and<br>GPIO_PUL_SEL[5] bits. |

| GPIO6    | I/O | SWC               | Ν                        | SWC                              | Drive strength controlled by GPIO_DS[6] bit. Pull<br>Enable/Polarity controlled by GPIO_PUL_EN[6] and<br>GPIO_PUL_SEL[6] bits. |

| GPIO7    | I/O | SWC               | Ν                        | SWC                              | Drive strength controlled by GPIO_DS[7] bit. Pull<br>Enable/Polarity controlled by GPIO_PUL_EN[7] and<br>GPIO_PUL_SEL[7] bits. |

| GPIO8    | I/O | SWC               | Ν                        | SWC                              | Drive strength controlled by GPIO_DS[8] bit. Pull<br>Enable/Polarity controlled by GPIO_PUL_EN[8] and<br>GPIO_PUL_SEL[8] bits. |

### Table 3-2. MCR20A Digital Signals Properties (continued)

1. Slew Rate Controlled: N=No; SWC=software-controlled

2. Internal pullup/pulldown device: N=No; SWC=software-controlled

## 3.9 Transceiver RF Configurations and External Connections

The MCR20A transceiver radio has features that enable a flexible and low cost RF interface:

- Programmable output power from -35 dBm to +8 dBm. This allows the user to set the power based on their specific applications minimizing current consumption while maximizing battery life.

- -102 dBm (typical) receive sensitivity At 1% PER, 20-byte packet (well above IEEE 802.15.4 specification of -85 dBm).

- Integrated transmit/receive (T/R) switch for low cost operation With internal PAs and LNA, the internal T/R switch allows a minimal part count radio interface using only a single balun to interface to a single-ended antenna.

## 3.9.1 RF Interface Pins

The following figure shows the RF interface pins and the associated analog blocks. The MCR20A radio is a differential transceiver architecture that has two (2) I/Os that support both receive and transmit functionality. Specifically, these I/Os are opposite in phase and will require off-chip matching for optimal performance. Because RF\_OUTP and RF\_OUTN ports are shared and duplexed, matching networks will need to accommodate both modes of operation.

Figure 3-3. RF Interface Pins

### 3.9.1.1 Antenna Diversity

Fast Antenna diversity (FAD) is supported in hardware through use of the four (4) dedicated control pins by register setup and control selection. They are ANT\_A, ANT\_B, RX\_SWITCH, and TX\_SWITCH. These switches, powered by VBAT, are programmable to sink and source two (2) levels of current (2 - 3 mA and 10 mA) or can operate in a high impedance mode. Each I/O will have a buffered feature with adjustable slew rate capability. Unless overridden by software, the last-good-antenna-selection (based on a successful preamble detect), is locked in place for TX sequences, as well as CCA and Energy Detect sequences. The hardware-selected antenna will not change again until the next RX preamble detection.

# 3.9.1.2 Fast Antenna Diversity (FAD)

The following system factors can be considered when configuring FAD for end applications:

#### Transceiver RF Configurations and External Connections

- With Fast Antenna Diversity, sensitivity performance increases the low-end limit of the dynamic range of the system.

- There is little cost of FAD which is essentially enabling the functionality and adding the circuitry for situations where the application runs the possibility of operating at the limits of RX sensitivity.

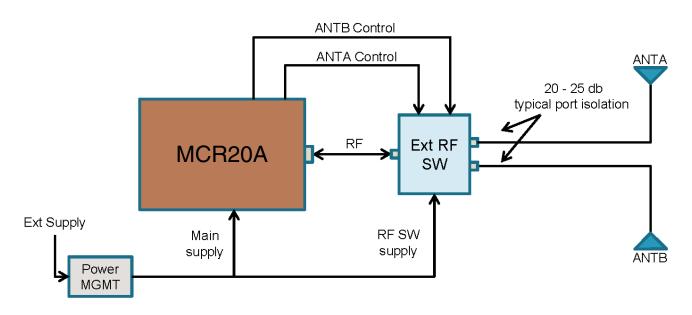

The next figure shows a simplified block diagram of the two port antenna control topology.

Figure 3-4. FAD control simplified block diagram

FAD Control Register Setup

The following registers allow setup, control and enable of the Fast Antenna Diversity (FAD) feature:

Antenna PAD Control (Indirect Modem\_ANT\_PAD\_CTRL, 0x30): This register sets the action on the pads ANTA, ANTB, RX\_SWITCH and TX\_SWITCH.

Set bit field ANTX\_EN [1:0] to proper selection for end application (default is 0).

- ANTA and ANTB switch signal during the preamble phase of the receive cycle.

- RX\_SWITCH and TX\_SWITCH switch during the receive and transmit cycle respectively.

Miscellaneous Pad Control (Indirect Modem\_MISC\_PAD\_CTRL, 0x31): This register sets the pad drive strength for ANTA, ANTB, RX\_SWITCH and TX\_SWITCH.

Bit[0] = 0 (default) for normal drive strength.

Antenna AGC and FAD Control (Indirect Modem\_ANT\_AGC\_CTRL, 0x51): This register controls the FAD feature.

Enable bit field [0] to 1 - Turns FAD on (default is 0).

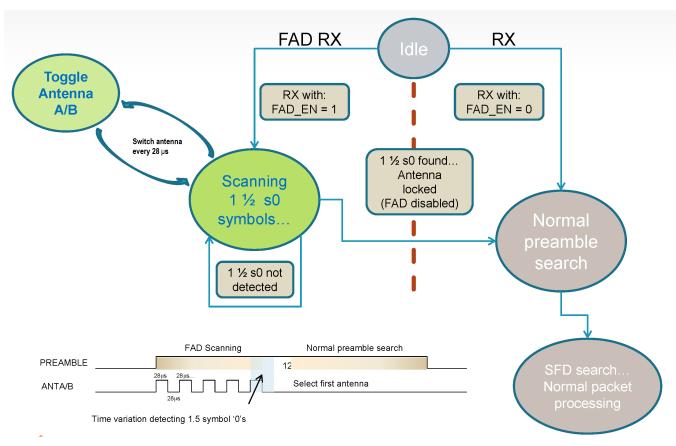

The following figure shows the flow and timing diagram from the idle state when the receiver takes either the FAD RX flow or the standard RX flow:

Figure 3-5. FAD flow and timing diagram

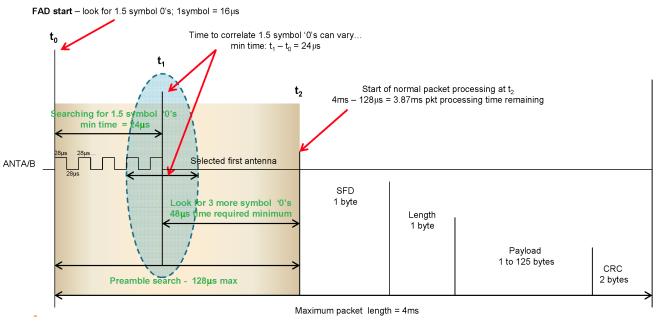

### FAD and Packet Timing

Packet timing with FAD enabled with two external antenna's A and B.

During the time period t1 - t0, the antenna's are switching at a rate of 28 µs.

- The circular region shows the timing variation while detecting 1.5 symbol '0's and is a function of system sensitivity level.

- At t1, the 'first' antenna meeting the 1.5 symbol '0' criteria is selected ... 3 more symbol '0's are then detected to complete the preamble search.

Normal packet processing follows a good preamble match

• The preamble period  $t^2 - t^0$  is fixed at 128 µs of the total packet cycle time – if a valid preamble is not found during this period, the receiver will start a new RX cycle.

**Transceiver RF Configurations and External Connections**

Figure 3-6. FAD preamble and packet timing

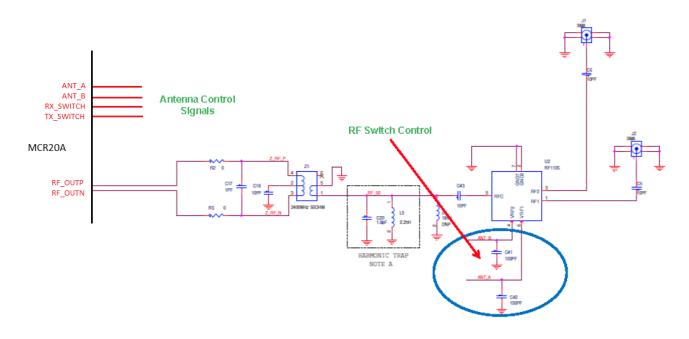

The next figure shows a typical FAD control pin design topology

### Figure 3-7. Typical circuitry for a two-antenna external switch design

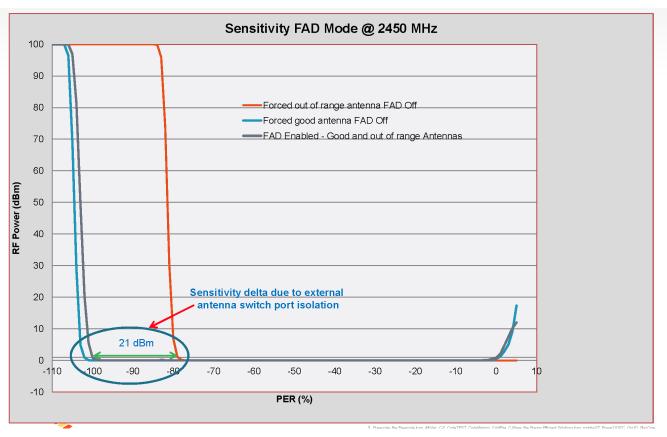

The following figure shows a simulated out of range antenna scenario when using the isolation through an RF switch to offset the RF signal by 21 dBm. The following sensitivity performance summary explains non-FAD and FAD Enabled Sensitivity Improvement.

**Chapter 3 System Considerations**

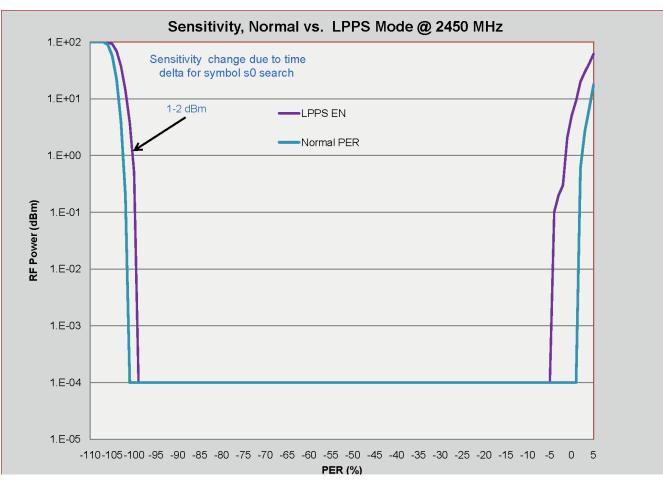

Figure 3-8. Sensitivity FAD mode at 2450 MHz

Sensitivity Performance Summary

Non-FAD mode

- By purposely choosing the bad antenna (out of range RF signal) it can be seen (orange curve) that the sensitivity is shifted to -78 dBm.

- By purposely choosing the good antenna (RF signal in range) it can be seen (blue curve) that the sensitivity is normal.

- The sensitivity delta is due to the isolation characteristics of the external RF switch component. This is the basic limitation of the system. The isolation of the RF switch ports in most cases is between 20-25 dB.

With FAD enabled (purple curve): With one antenna out of range and the other antenna good, the sensitivity is NOW in the normal range (about -99 dBm or better).

- Sensitivity performance is impacted by 1-2 dB in FAD mode vs. an ideally placed antenna but overall PER performance is significantly increased vs. having a single antenna with poor placement.

- Within the dynamic range of the receiver, sensitivity in FAD mode does not impact performance and therefore is not discernible to the user.

#### Transceiver RF Configurations and External Connections

- Outside the dynamic range of the receiver is where FAD will help system performance and will have noticeable improvements to the system.

- Unless overridden by software, the last-good-antenna-selection (based on a successful preamble detect), is locked in place for TX sequences as well as CCA and Energy Detect sequences. The hardware-selected antenna will not change again until the next RX sequence.

## 3.9.2 **RF Output Power Distribution**

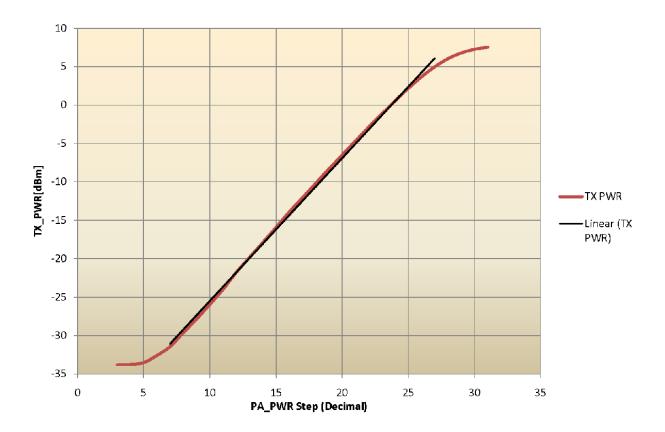

The following figure shows the linear region of the output and the typical power distribution of the radio as a function of PA\_PWR [4:0] range. The PA\_PWR [4:0] is the lower 5 bits of the PA\_PWR 0x23 direct register and has a usable range of 3 to 31 decimal.

Figure 3-9. MCR20A transmit power vs. PA\_PWR step

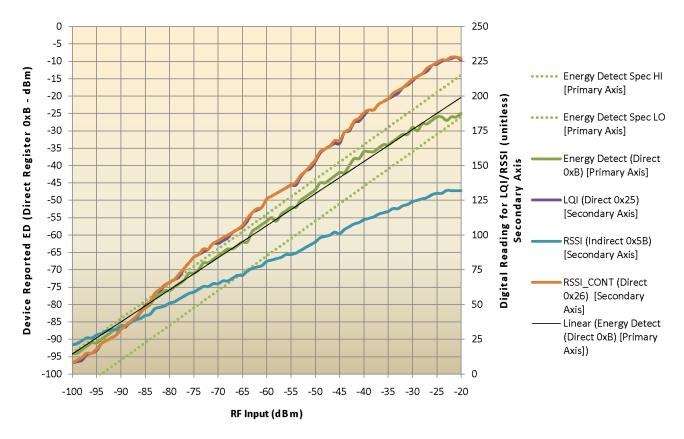

# 3.9.3 LQI ED RSSI

The following figure shows the devices reported Energy Detect (ED) as a function of input power. The figure also shows the Link Quality Indication (LQI)/RSSI\_CONT (continuous) and the RSSI (Received Signal Strength Indication) as a function of a unitless numeric register reading. LQI is available 64 µs after the preamble is detected. RSSI\_CONT can be used to read LQI if a continuous value averaged over the entire received packet is desired. This value may be read as LQI if continuous update of LQI is desired during packet reception (both scaled the same but averaged differently). The curves are measured using the default offset compensation value and can be changed to center the curve if desired.

The following sequeces are performed in test software to create curves in the figure otherwise similar sequences are incorporated into our software stacks:

- For ED, device is configured to perform an ED via write to the register 0x7 with 0x00

- ED/CCA sequence is started via write to register 0x3 with 0x3

- Register 0 is polled for bit 3 to be set

- RSSI\_CONT\_EN bit is disabled in Indirect 0x25 (CCA\_CTRL) all other bits are reset/overwrite values

- direct register 0x0B is read (CCA Final)

- direct register 0x25 is read (LQI)

- indirect register 0x5B is read (RSSI)

- direct register 0x26 is read (RSSI\_CONT) [not enabled in ED case so ignored]

- For LQI, device is configured to perform an LQI via write to the register 0x7 with 0x00

- Device is configured to perform an LQI via write to the register 0x7 with 0x00

- RX sequence is started via write to register 0x3 with 0x1

- Register 0 is polled for bit 2 to be set

- RSSI\_CONT\_EN bit is Enabled in Indirect 0x25

- RSSI\_CONT\_EN bit is disabled in Indirect 0x25 (CCA\_CTRL) all other bits are reset/overwrite values

- Direct register 0x0B is read (CCA Final)

- Direct register 0x25 is read (LQI)

- Indirect register 0x5B is read (RSSI)

- Direct register 0x26 is read (RSSI\_CONT) [Valid for LQI]

For both LQI and ED the input power is swept with a modulated input signal from -100 dBm to -20 dBm in steps of 1 dBm and the above sequences are called for each step and results recorded.

From the figure above, an equation can be derived as follows. Using Y(LQI) and X(RF), the minimum and maximum values from the figures secondary axis are determined as:

| LQI                             | Y(LQI) | X(RF) |

|---------------------------------|--------|-------|

| Maximum                         | 225    | -25   |

| Minimum                         | 12     | -100  |

| Point near middle Dynamic Range | 125    | -60   |

### Table 3-3. Minimum and Maximum Values

Therefore the slope = 2.84 and B = 295.4. So to convert the 8-bit unitless number read from direct register 0x25 to an ideal RF equivalent, use the following equation:

RF = (LQI - 295.4) / 2.84

# 3.10 Timer Resources

When writing software applications, the user should be aware of the set of timer resources available.

## 3.10.1 Modem Event Timer

The MCR20A transceiver contains an internal Event Timer block whose clock is derived from a programmable prescaler which is driven by the 32 MHz crystal source. The Event Timer consists of the prescaler and a 24-bit counter which increment whenever the modem crystal clock is operating. The Event Timer provides the following functions:

- The 24-bit counter generates "current" system time The counter runs continuously when the modem is not in a low power mode and provides a local "current" time. The present value can be read from the EVENT\_TMR\_USB/MSB/LSB registers. A counter frequency of 250 kHz is used. The counter value is used to generate a time stamp for received frames and is also used for comparison to four different comparators that allow up to four different time delays

- Interrupt generation at pre-determined system times There are four comparator functions that can generate an interrupt to the MCU when the value of the comparator matches the system counter. These function as timers to generate time delays or trigger events and can augment the MCU timers for generating time delays required within the 802.15.4 application software

- Exit from Doze Mode at pre-determined system time Timer comparator Tmr\_Cmp2 can be used to wake-up the modem from low power Doze Mode

- Latches "timestamp" value during packet reception With every received frame, there is a timestamp generated and stored in a modem SPI register. The timestamp is taken from the counter when the frame length indicator (FLI) is received

- Initiates timer-triggered sequences The modem has three basic active modes of RX, TX, and CCA. Each of these sequences can be timer-triggered to become active after a set delay based on timer comparator Tmr\_Cmp2. This feature can be useful for implementing 802.15.4 application sequences

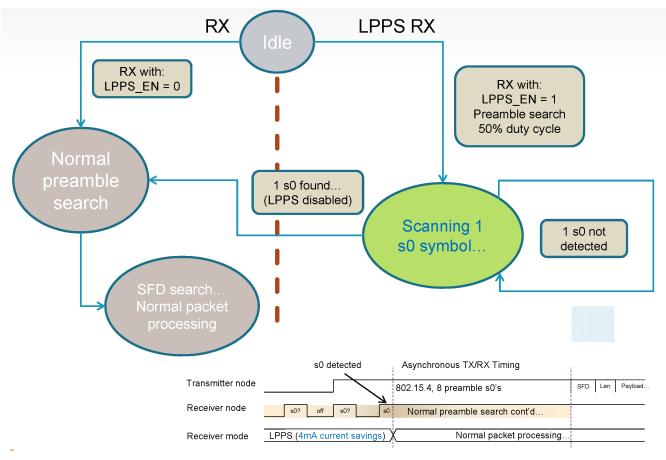

# 3.11 Low Power Considerations