# AN13057

# Understanding Cap Bank in LPC55(S)xx

Rev. 0 — 16 November 2020 Application Note

by: NXP Semiconductors

## 1 How to read the application note

All LPC55(S)xx products have two crystal oscillators: A 16 MHz crystal oscillator and a 32 KHz crystal oscillator.

Each crystal oscillator has one embedded capacitor bank, which is always enabled and its capacitance can be adjusted in certain range (IEC equivalent capacitive load: 6 - 10 pF). The capacitor bank can be used as integrated load capacitors for the crystal oscillators, which helps save external load capacitors of the crystal and hence the system BOM cost.

This application note provides a short introduction to this capacitor bank or **Cap Bank**, and describes how to apply this function to the actual design.

## 2 Advantage of embedded Cap Bank

The advantages of the embedded Cap Bank are as follows:

- · Conserves component area on the PCB.

- · Saves Bill of Materials (BOM).

- Maintains a Capacitive Load (CL) between 6 10 pF (IEC equivalent).

- Relies on simple APIs to configure the Capacitor Banks based on the crystal Capacitive Load (CL) and measured PCB

parasitic capacitances on the XIN and XOUT pins.

# 3 Understanding Cap Bank

#### 3.1 Cap Bank block diagram

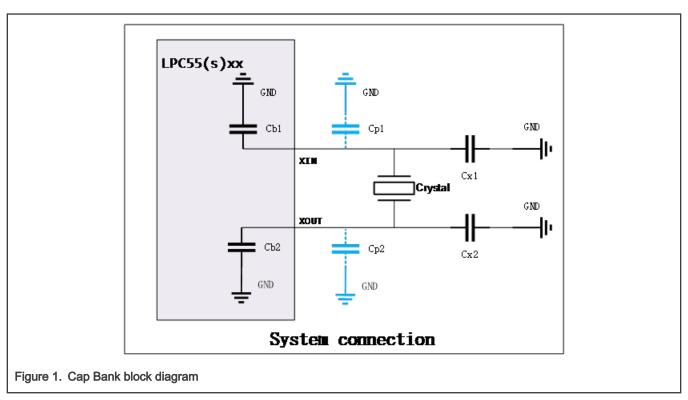

The following figure shows the equivalent internal Cap Bank block with a standard crystal connection diagram.

#### Contents

| 1<br>2 | How to read the application note Advantage of embedded Cap Bank |   |

|--------|-----------------------------------------------------------------|---|

|        |                                                                 | 1 |

| 3      | Understanding Cap Bank                                          | 1 |

| 3.1    | Cap Bank block diagram                                          | 1 |

| 3.2    | Cap Bank specification in                                       |   |

|        | LPC55(S)xx                                                      | 2 |

| 4      | Use cases                                                       | 2 |

| 4.1    | Use case 1: CL (or CLtot_IEC) =                                 |   |

|        | 8pF, Cp1 = 2pF, Cp2 = 3pF                                       | 3 |

| 4.2    | Use case 2: external crystal load                               |   |

|        | capacitor needed                                                | 3 |

| 5      | Capacitor Banks API description                                 | 3 |

| 5.1    | API routines                                                    | 5 |

| 5.2    | API usage examples                                              | 5 |

| 6      | SDK example                                                     |   |

| 6.1    | Hardware preparation                                            | 9 |

| 6.2    | Software configuration10                                        |   |

| 6.3    | Demo12                                                          |   |

| 7      | Conclusion14                                                    |   |

|        |                                                                 |   |

- Cb1, Cb2: Total equivalent capacitor including capacitor bank, package, and pad parasitic capacitors in MCU in single ended mode (i.e., on single crystal pin)

- Cp1, Cp2: Equivalent PCB parasitic capacitances on the PCB board in single ended mode

- Cx1, Cx2: User external crystal load capacitors used in single ended mode (i.e., on each crystal pin)

The single ended total capacitive load seen by the external crystal:

CLtot\_se1= Cb1 +Cp1+Cx1; (tot is short for total)

CLtot\_se2= Cb2 +Cp2+Cx2;

The total IEC equivalent capacitive load seen by the external crystal (or CL) is the series of both single ended total capacitive loads:

CLtot\_IEC= CL = (CLtot\_se1\* CLtot\_se2)/(CLtot\_se1+ CLtot\_se2).

#### 3.2 Cap Bank specification in LPC55(S)xx

- · Cb1 and Cb2 are equal.

- Cb1 or Cb2 is 12pF 20pF, so the range of IEC equivalent crystal load capacitance value for internal Cap Bank is 6pF 10pF.

- The reset value (default value) of Cb1 or Cb2 is 12pF, so the reset IEC equivalent crystal load capacitance is 6pF.

- · All these values are guaranteed at factory across the device working temperature range.

#### 4 Use cases

Crystal Load capacitance (CL) value can be easily found in the crystal data sheet. For example, 6pF, 8pF, 10pF, 12pF, and so on. The aforementioned CLtot IEC, total IEC equivalent capacitive load needed for crystal is equal to CL.

Firstly, CLtot\_IEC (or CL) needs to be converted into single ended total capacitive value as follows:

CLtot\_se1 = CLtot\_se2 = 2\*CLtot\_IEC = 2\* CL

Secondly, the parasitic capacitances of the PCB (Cp1 and Cp2) related to the crystal on the PCB board need be measured.

Application Note 2/15

Then the following results are calculated:

The following sections shows different configurations of Cb1/2 and Cx1/2 for different use cases.

#### 4.1 Use case 1: CL (or CLtot\_IEC) = 8pF, Cp1 = 2pF, Cp2 = 3pF

Assume a crystal with load capacitance (CL) of 8pF is used, then

$$Cb2 + Cx2 = CLtot_se2 - Cp2 = CL - Cp2 = 2*8pF - 3pf = 13pF;$$

Because the range of Cb1 and Cb2 values are 12pF - 20pF, which already covers the above calculated expected capacitance 14pF/13pF, the Cx1 and Cx2 values can be zero. In other words, there is no need to add Cx1 and Cx2 on PCB. This can save components and PCB area.

Therefore, just configure Cb1 = 14pF, Cb2 = 13pF. Because Cb1 and Cb2 are equal in LPC55(S)xx, the maximum value between them is taken normally.

Therefore, Cb1 = Cb2 = 14pF.

#### 4.2 Use case 2: external crystal load capacitor needed

Assume a crystal with load capacitance (CL) of 15pF is used, then

Because the range of Cb1 and Cb2 values are 12pF - 20pF, which is below the above calculated expected capacitance 28pF, the Cx1 and Cx2 are needed. In other words, Cx1 and Cx2 must be added on PCB.

In this case, the recommended values of Cb1 and Cb2 are taken as 16pF normally,

Therefore, Cx1/x2 can be derived as follows:

$$Cb1 = Cb2 = 16pF$$

$$Cx1 = Cx2 = 28pF - 16pF = 12pF$$

#### NOTE

If Cap Bank is not configured, Cb1 and Cb2 keep the default value, which is 12pF.

In this case, Cx1/x2 can be derived as follows:

$$Cx1 = Cx2 = 28pF - 12pF = 16pF$$

# 5 Capacitor Banks API description

Capacitor banks API routines are used to configure the Cap Bank values of Cb1 and Cb2.

For user convenience, it only requires users to provide Cbp, Cp1, and Cp2.

Here, Cbp is the actual IEC equivalent load capacitance from crystal point of view without extra capacitors Cx1, Cx2, that is, Cbp is:

$$Cbp = (Cb1+Cp1) * (Cb2+Cp2)/((Cb1+Cp1) + (Cb2+Cp2))$$

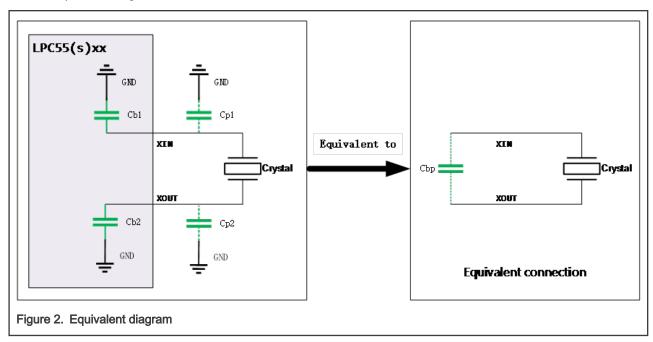

1. If Cbp = CL, it does not need to add external crystal load capacitor Cx1 and Cx2. That is, if there is no need to add external crystal load capacitor Cx1 and Cx2 per use case 1 in section 4.1 (i.e., CL is within the range of 6 - 10 pF), then the Cbp is equal to total IEC equivalent capacitive load CLtot\_IEC or the crystal load capacitance CL:

See the equivalent diagram below.

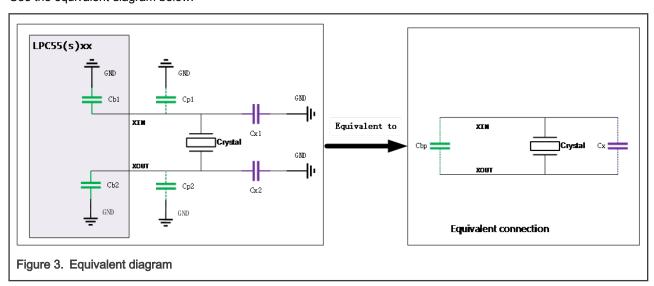

2. If Cbp < CL, then the external crystal load capacitance Cx must be added. That is, if there is need to add Cx1 and Cx2 per use case 2 in section 4.2, and Cbp + Cx = CLtot\_IEC = CL, Where Cx = (Cx1\* Cx2)/ (Cx1+ Cx2), then the external load capacitance Cx can be derived by: Cx = CL – Cbp.

Assume Cx1 = Cx2, then Cx1 = Cx2 = 2\*Cx = 2\*(CL - Cbp).

In this case, it is recommended that the internal Cap Bank value Cb1, Cb2 = 16 pF.

See the equivalent diagram below.

Cp1 and Cp2 are related to the board, the user needs to provide their values to the Cap Bank API function as the second and third parameters after measurement.

CL can be found in the crystal data sheet, so Cbp can be easily derived as mentioned previously and passed to the Cap Bank API routine as the first parameter.

#### 5.1 API routines

There is only one routine for each crystal oscillator as follows.

Table 1. API routines

| Function prototype                                                                                                                                             | API description                                                                                                                                                                                                                                                          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| void POWER_Xtal16mhzCapbankTrim(int32_t<br>pi32_16MfXtallecLoadpF_x100, int32_t<br>pi32_16MfXtalPPcbParCappF_x100, int32_t<br>pi32_16MfXtalNPcbParCappF_x100); | This API configures the internal Capacitor Bank of the 16 MHz crystal oscillator, where parameters:  pi32_16MfXtallecLoadpF_x100: <b>Cbp</b> (pF) x 100;  pi32_16MfXtalPPcbParCappF_x100: <b>Cp1</b> (pF) x 100;  pi32_16MfXtalNPcbParCappF_x100: <b>Cp2</b> (pF) x 100; |  |  |

| void POWER_Xtal32mhzCapbankTrim(int32_t<br>pi32_32kfXtallecLoadpF_x100, int32_t<br>pi32_32kfXtalPPcbParCappF_x100, int32_t<br>pi32_32kfXtalNPcbParCappF_x100); | This API configures the Capacitor Bank of the 32 KHz crystal oscillator, where parameters:  pi32_32kfXtallecLoadpF_x100: <b>Cbp</b> (pF) x 100;  pi32_32kfXtalPPcbParCappF_x100: <b>Cp1</b> (pF) x 100;  pi32_32kfXtalNPcbParCappF_x100: <b>Cp2</b> (pF) x 100;          |  |  |

In each routine, there are three parameters needed (Cbp, Cp1, Cp2). The unit of parameters is one hundredth pF.

For example, if

Cbp = 8.5pF, Cp1 = 2pF, Cp2 = 3pF.

Then, the call to API should be POWER\_Xtal16mhzCapbankTrim (850,200,300).

#### 5.2 API usage examples

This section explains the API usage examples described in the device's user manual.

#### 5.2.1 16 MHz Crystal Oscillator

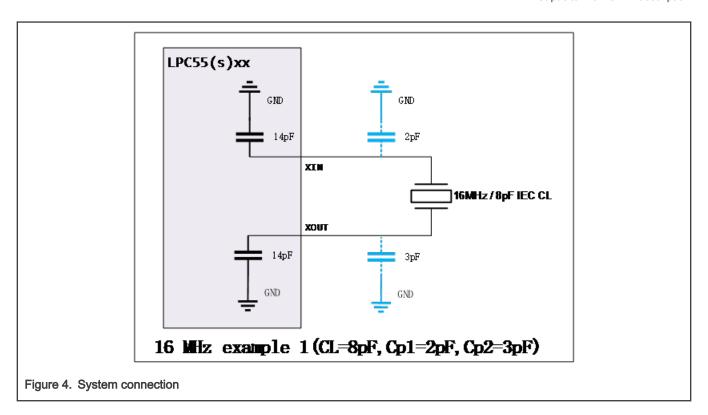

5.2.1.1 Example 1: 8pF IEC Capacitance Load, 2pF PCB parasitic capacitance on XIN pin, 3pF PCB parasitic capacitance on XOUT pin.

According to the conditions of this example, CLtot\_IEC, Cp1/p2 are:

$CLtot_IEC = CL = 8pF, Cp1 = 2pF, Cp2 = 3pF.$

Because CL is within the range of 6 - 10 pF, it does not need to add external crystal load capacitor Cx1 and Cx2, and the Cbp is equal to CL = 8pF.

Therefore, the call to Cap Bank API routine should be: XTAL\_16mhz\_capabank\_trim(8 \* 100, 2 \* 100, 3 \* 100).

NOTE Cb1 should be equal to Cb2 and be set to the maximum value of Cb1 and Cb2.

The system connection as follows:

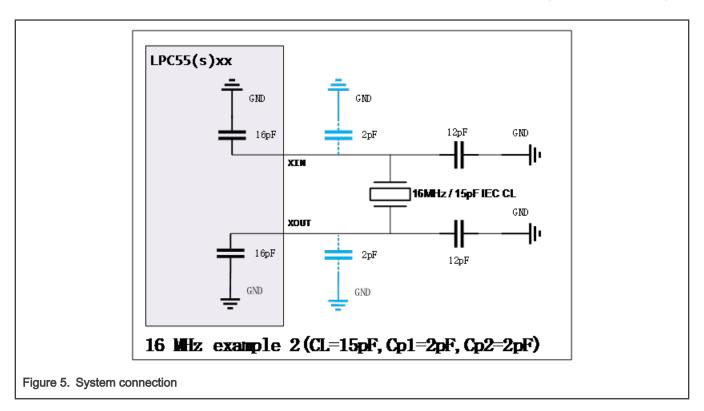

# 5.2.1.2 Example 2: 15pF IEC Capacitance Load, 2pF PCB parasitic capacitance on XIN pin, 2pF PCB parasitic capacitance on XOUT pin.

According to the conditions of this example, CLtot\_IEC, Cp1/p2 are:

$CLtot_IEC = CL = 15pF, Cp1 = 2pF, Cp2 = 2pF.$

Because CL exceeds 10 pF, external crystal load capacitance Cx must be added.

In another words, the user needs to add Cx1 and Cx2 per use case 2 in Section 4.2.

Cbp + Cx = CLtot\_IEC = CL;

Then, the external load capacitance Cx can be derived by:

Cx = CL - Cbp:

Assume Cx1 = Cx2, then Cx1 = Cx2 = 2\*Cx = 2\*(CL - Cbp)

In this case, it is recommended that the internal Cap Bank value Cb1, Cb2 = 16pF.

Therefore:

Cbp = (Cb1+Cp1) \* (Cb2+Cp2)/((Cb1+Cp1) + (Cb2+Cp2)) = 9pF.

Cx1 = Cx2 = 2\*Cx = 2\*(CL - Cbp)=12pF.

The call to Cap Bank API routine should be: XTAL\_16mhz\_capabank\_trim(9 \* 100, 2 \* 100, 2 \* 100);

The system connection as follows:

# 5.2.2 32 KHz Crystal Oscillator

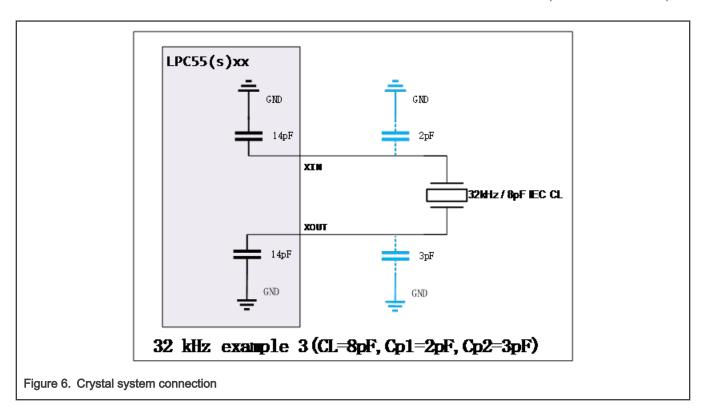

5.2.2.1 Example 3: 8pF IEC Capacitance Load, 2pF PCB parasitic capacitance on XIN pin, 3pF PCB parasitic capacitance on XOUT pin.

This is the same as example 1 aforementioned.

Therefore, the call to Cap Bank API routine should be: XTAL\_32kHz\_capabank\_trim(8 \* 100, 2 \* 100, 3 \* 100);

it docs not need to add extra capacitors on PCB.

The crystal system connection is as follows:

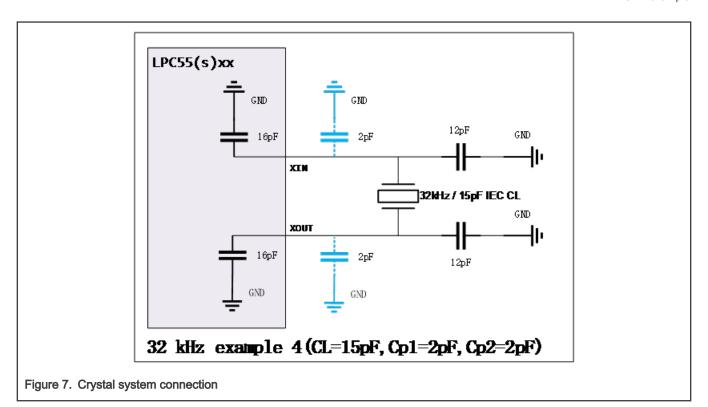

5.2.2.2 Example 4: 15pF IEC Capacitance Load, 2pF PCB parasitic capacitance on XIN pin, 2pF PCB parasitic capacitance on XOUT pin.

This is the same as example 2 aforementioned.

Therefore, the call to Cap Bank API routine should be: XTAL\_32kHz\_capabank\_trim(9 \* 100, 2 \* 100, 2 \* 100);

And the user needs to add extra capacitors on PCB: Cx1 = Cx2 = 12pF.

The crystal system connection is as follows:

## 6 SDK example

Here is an example code that shows how to configure the internal Cap Bank, and how to fine tune it to achieve the best accuracy of crystal oscillator output on the existing PCB.

#### 6.1 Hardware preparation

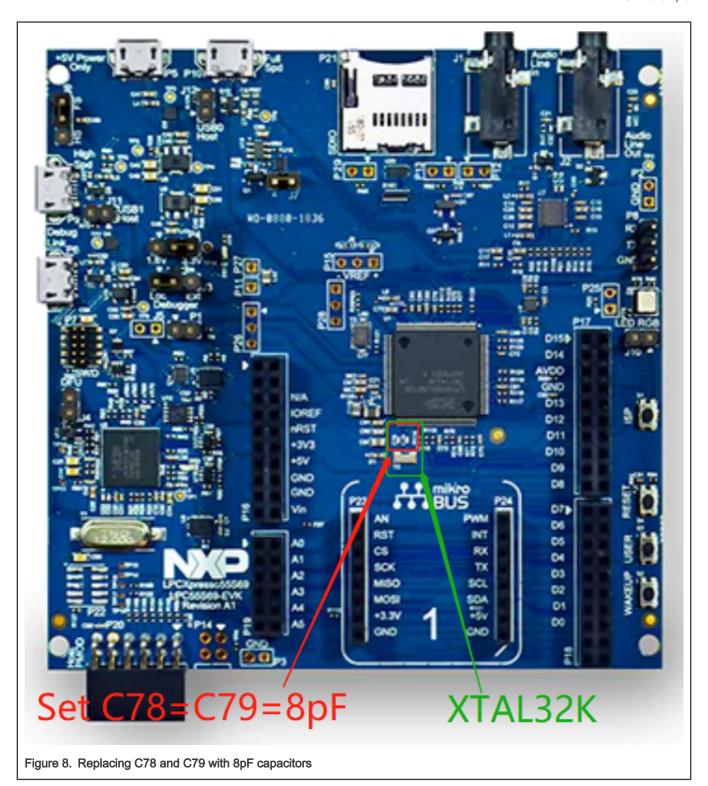

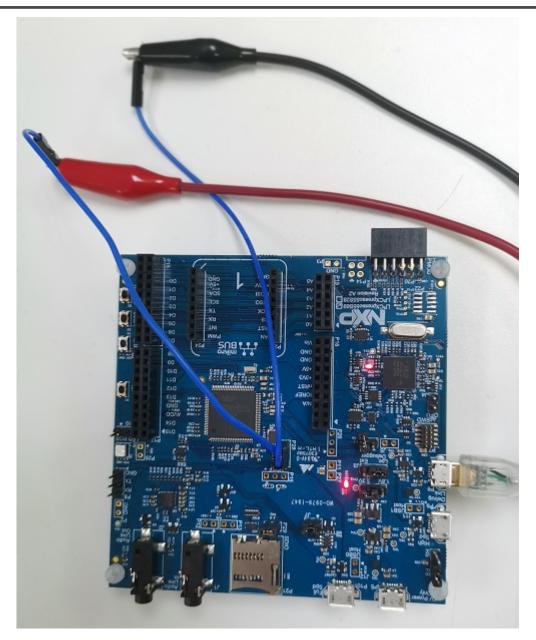

There are two external crystal oscillators on the board: 16 MHz and 32.768 KHz. This application note uses 32.768 KHz as an example to describe how to configure the Cap Bank function.

The part number of the 32k crystal on the EVK board is NX3215SA-32.768K-STD-MUS-2. It can be concluded from the manual that its IEC Capacitance Load (CL) is 12.5 pF, which does exceed the Cap Bank trim range of LPC5500 (6 – 10 pF).

Therefore, Cbp < CL, and the external crystal load capacitance Cx must be added. In another words, the user needs to add Cx1 and Cx2 per use case 2 in Section 4.2, and

Cbp + Cx = CLtot\_IEC = CL;

Where Cx = (Cx1\*Cx2)/(Cx1+Cx2).

Then, the external load capacitance Cx can be derived by:

Cx = CL - Cbp;

Assume Cx1 = Cx2, then Cx1 = Cx2 = 2\*Cx = 2\*(CL - Cbp).

In this case, it is recommended that the internal Cap Bank value Cb1, Cb2 = 16 pF, and Cp1 = 1pF, Cp2 = 1pF.

Therefore,

Cbp = (Cb1+Cp1) \* (Cb2+Cp2)/((Cb1+Cp1) + (Cb2+Cp2)) = 8.5pF.

Cx1 = Cx2 = 2\*Cx = 2\*(CL - Cbp) = 8pF.

The call to the Cap Bank API routine should be: XTAL\_16mhz\_capabank\_trim(850, 100, 100);

That is, user needs to replace C78 and C79 with 8pF capacitors on the board as the following picture shows.

Application Note 9 / 15

# 6.2 Software configuration

To configure the Cap Bank and easily check the results, users need to configure 32KHz Crystal Oscillator (XTAL32K) and CLKOUT function, output the trimmed clock directly to the clkout pin, and measure the result with a high-precision instrument.

The following code snippet shows how to configure the Cap Bank and route the crystal oscillator output to the CLKOUT pin:

SDK example

```

int main (void)

char ch;

/* Init board hardware. */

/* set BOD VBAT level to 1.65V */

POWER SetBodVbatLevel(kPOWER BodVbatLevel1650mv, kPOWER BodHystLevel50mv, false);

/* attach main clock divide to FLEXCOMMO (debug console) */

CLOCK AttachClk(BOARD DEBUG UART CLK ATTACH);

BOARD InitPins();

BOARD BootClockFROHF96M();

BOARD InitDebugConsole();

PRINTF("capbank configuration demo, please capture the clkout frequency.\r\n");

while (1)

}

IOCON->PIO[0][16] = ((IOCON->PIO[0][16] &

/* Mask bits to zero which are setting */

(~(IOCON PIO FUNC MASK | IOCON PIO MODE MASK | IOCON PIO DIGIMODE MASK)))

/* Selects pin function.

* : PORT016 (pin 14) is configured as CLKOUT. */

| IOCON_PIO_FUNC(PIOO_16_FUNC_ALT2)

/* Selects function mode (on-chip pull-up/pull-down resistor control).

* : Pull-up.

* Pull-up resistor enabled. */

| IOCON PIO MODE(PIOO 16 MODE PULL UP)

/* Select Digital mode.

* : Enable Digital mode.

* Digital input is enabled. */

| IOCON_PIO_DIGIMODE(PIOO_16_DIGIMODE_DIGITAL));

```

Understanding Cap Bank in LPC55(S)xx, Rev. 0, 16 November 2020

Application Note 11 / 15

```

void BOARD BootClockFROHF96M(void)

#ifndef SDK SECONDARY CORE

/*!< Set up the clock sources */

/*!< Configure FR0192M */

POWER_DisablePD(kPDRUNCFG_PD_FR0192M);

/*!< Ensure FRO is on */

CLOCK SetupFROClocking(12000000U);

/*!< Set up FRO to the 12 MHz, just for sure */

/*!< Switch to FRO 12MHz first to ensure we can change the clo

CLOCK AttachClk(kFRO12M to MAIN CLK);

/* Enable FRO HF(96MHz) output */

CLOCK SetupFROClocking(96000000U);

POWER Xtal32khzCapabankTrim(850, 100, 100); Set Cbp=8.5pF,Cp1=Cp2=1pF.

/*!< Configure RTC OSC */

POWER DisablePD(kPDRUNCFG PD XTAL32K):

/*!< Powered the XTAL 32 kHz RTC oscillator */

/*!< Powered down the FRO 32 kHz RTC oscillator */

POWER EnablePD(kPDRUNCFG PD FRO32K);

CLOCK AttachClk(kXTAL32K to OSC32K);

/*!< Switch OSC32K to XTAL32K */

CLOCK EnableClock(kCLOCK Rtc);

/*!< Enable the RTC peripheral clock */

Set XTAL32K /*!< Make sure the reset bit is cleared */

RTC->CTRL &= ~RTC CTRL SWRESET MASK;

POWER_SetVoltageForFreq(96000000U);

/*!< Set voltage for the one of the fastest clock outputs: Sys

CLOCK SetFLASHAccessCyclesForFreq(96000000U);

/*!< Set FLASH wait states for core */

/*!< Set up dividers */

CLOCK_SetClkDiv(kCLOCK_DivArmTrClkDiv, OU, true);

/*!< Reset TRACECLKDIV divider counter and halt it

/*!< Set TRACECLKDIV divider to value 1 */

CLOCK SetClkDiv(kCLOCK DivArmTrClkDiv, 1U, false);

CLOCK_SetClkDiv(kCLOCK_DivSystickClk0, 0U, true);

/*!< Reset SYSTICKCLKDIV0 divider counter and halt

CLOCK SetClkDiv(kCLOCK DivSystickClk0, 1U, false);

/*!< Set SYSTICKCLKDIV0 divider to value 1 */

CLOCK SetClkDiv(kCLOCK_DivSystickClk1, 0U, true);

/*!< Reset SYSTICKCLKDIV1 divider counter and halt</pre>

/*!< Set SYSTICKCLKDIV1 divider to value 1 */

CLOCK SetClkDiv(kCLOCK DivSystickClkl, 1U, false);

CLOCK SetClkDiv(kCLOCK DivAhbClk, 1U, false);

/*!< Set AHBCLKDIV divider to value 1 */

CLOCK SetClkDiv(kCLOCK DivAhbClk, OU, true);

/*!< Reset AHBCLKDIV divider counter and halt it */

/*!< Set AHBCLKDIV divider to value 1 */

CLOCK SetClkDiv(kCLOCK_DivAhbClk, 1U, false);

CLOCK_SetClkDiv(kCLOCK_DivClkOut, OU, true);

/*!< Reset CLKOUTDIV divider counter and halt it */

CLOCK SetClkDiv(kCLOCK DivClkOut, 00, 614e,,

CLOCK SetClkDiv(kCLOCK DivClkOut, 1U, false);

/*!< Set CLKOUTDIV divider to value 1 */

CLOCK SetClkDiv(kCLOCK DivFrohfClk, OU, true);

/*!< Reset FROHFDIV divider counter and halt it */

CLOCK SetClkDiv(kCLOCK DivFrohfClk, 1U, false);

/*!< Set FROHFDIV divider to value 1 */

/st!< Set up clock selectors - Attach clocks to the peripheries st/

/*!< Switch CLKOUT to OSC32K */ Set clkout source

CLOCK AttachClk(kOSC32K to CLKOUT);

/*!< Switch MAIN CLK to FRO HF */

CLOCK_AttachClk(kFRO_HF_to_MAIN_CLK);

/*< Set SystemCoreClock variable. */

SystemCoreClock = BOARD BOOTCLOCKFROHF96M CORE CLOCK;

#endif

```

#### 6.3 Demo

To see the demo result, a frequency meter such as HP 5313A Universal Counter shall be used.

Here assume Cp1=Cp2=1pF. Then the call to Cap Bank API is as follows:

#### POWER\_Xtal32khzCapabankTrim(Cbp\*100, 100, 100); by default Cbp = 8.5pF;

Now you can configure first parameter of this routine (Cbp) to different values other than the default value (8.5pF). Then rebuild and run the code above.

You can see crystal output frequency changes in the frequency meter with different Cbp as follows

Understanding Cap Bank in LPC55(S)xx, Rev. 0, 16 November 2020 12 / 15

Figure 9. Crystal output frequency (1)

Figure 10. Crystal output frequency (2)

Application Note 13 / 15

The following table summarizes the experimental results for different Cbp with same 32KB crystal on board (Cx1=Cx2=8pF).

Table 2. Experimental results for different Cbp with same 32KB crystal

| Experiment<br>Number | Code                                                 | Cbp<br>value | Frequency output (Hz) | Target (Hz) | Error<br>(ppm) |

|----------------------|------------------------------------------------------|--------------|-----------------------|-------------|----------------|

| 1                    | POWER_Xtal32khzCapabankTrim(600, 100, 100);          | 6 pF         | 32769.773             | 32768.000   | 54.108         |

| 2                    | POWER_Xtal32khzCapabankTrim( <b>700</b> , 100, 100); | 7 pF         | 32769.159             | 32768.000   | 35.370         |

| 3                    | POWER_Xtal32khzCapabankTrim(800, 100, 100);          | 8 pF         | 32768.583             | 32768.000   | 17.792         |

| 4                    | POWER_Xtal32khzCapabankTrim(850, 100, 100);          | 8.5 pF       | 32768.360             | 32768.000   | 10.986         |

| 4                    | POWER_Xtal32khzCapabankTrim(900, 100, 100);          | 9 pF         | 32768.146             | 32768.000   | 4.456          |

| 5                    | POWER_Xtal32khzCapabankTrim(1000, 100, 100);         | 10 pF        | 32767.724             | 32768.000   | 8.423          |

Based on the test result above, Cbp = 9pF can achieve the best accuracy of the oscillator output frequency toward the target frequency 32768 Hz, which is only 4.5 PPM deviation.

#### 7 Conclusion

The original intention of the built-in Cap Bank is to allow users to reduce BOM costs and PCB area. The original intention of Cap Bank's API function is to make it easy for users to configure the internal Cap Bank. These Cap Banks are always enabled, and their capacitance values have a certain adjustable range. In most cases, it is not exceeded. If external crystal's IEC load capacitance (CL) exceeds this range, please correctly understand the meaning of the first parameter(Cbp) of the API and calculate it according to the calculation methods shown in the aforementioned example 2 and example 4.

When designing a PCB board, ensure that the PCB traces are symmetrical, that is, Cp1=Cp2. Use SDK version 2.8.0 or newer, which can correctly support Cap Bank configuration.

Application Note 14 / 15

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC. MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platformin a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, eIQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2020.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 16 November 2020 Document identifier: AN13057